机构名称:

¥ 1.0

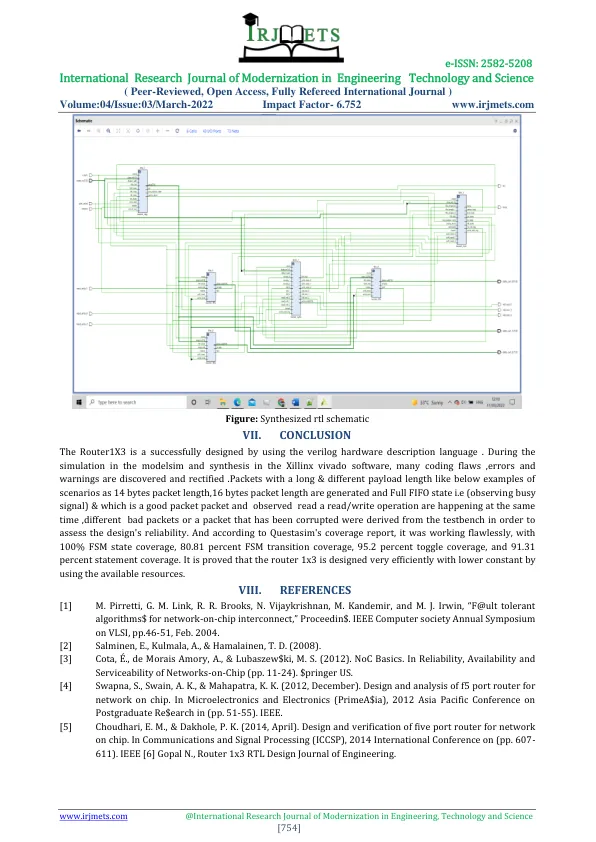

Router1X3 是使用 verilog 硬件描述语言成功设计的。在 modelsim 中的仿真和 Xillinx vivado 软件中的综合过程中,发现并纠正了许多编码缺陷、错误和警告。数据包具有较长且不同的有效载荷长度,如下面示例场景所示,数据包长度为 14 字节,数据包长度为 16 字节,且处于完整 FIFO 状态(即(观察忙信号))并且是好数据包,并且观察到读取/写入操作同时发生,从测试平台得出不同的坏数据包或已损坏的数据包,以评估设计的可靠性。根据 Questasim 的覆盖率报告,它运行完美,具有 100% 的 FSM 状态覆盖率、80.81% 的 FSM 转换覆盖率、95.2% 的切换覆盖率和 91.31% 的语句覆盖率。事实证明,路由器 1x3 的设计非常高效,并且利用了可用资源,常数较低。

使用 VERILOG 进行路由器 1X3 -RTL 设计