机构名称:

¥ 1.0

第一作者 Ragini Singh 是电子和通信工程师,目前正在印度博帕尔 (MP) RGPV 攻读微电子和 VLSI 设计硕士学位。第二作者 Sandip Nemade 教授拥有 VLSI 设计学位,目前担任印度博帕尔 (MP) 技术学院电子和通信系助理教授。

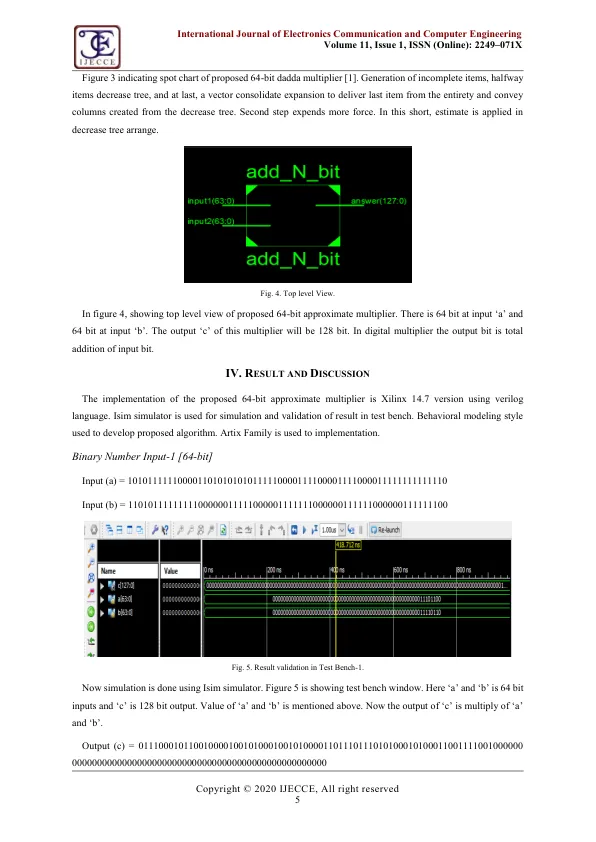

64 位近似乘法器的实现...