机构名称:

¥ 1.0

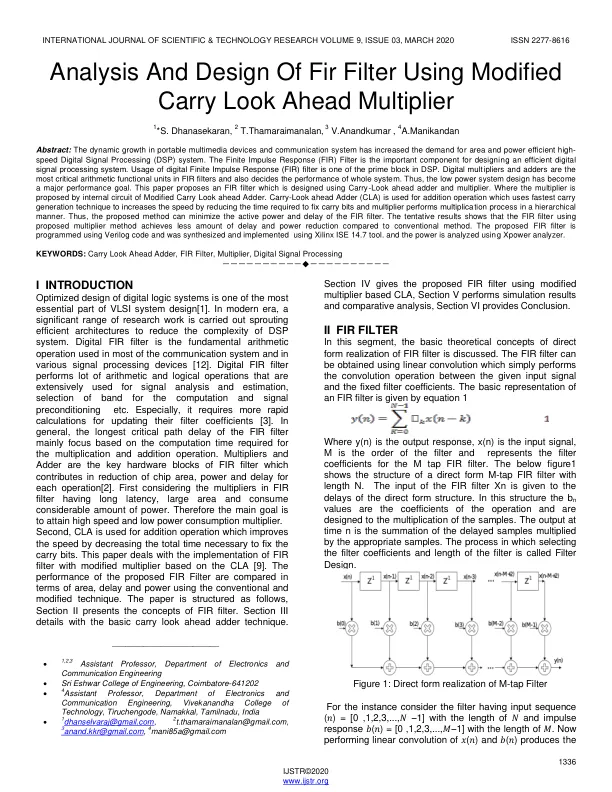

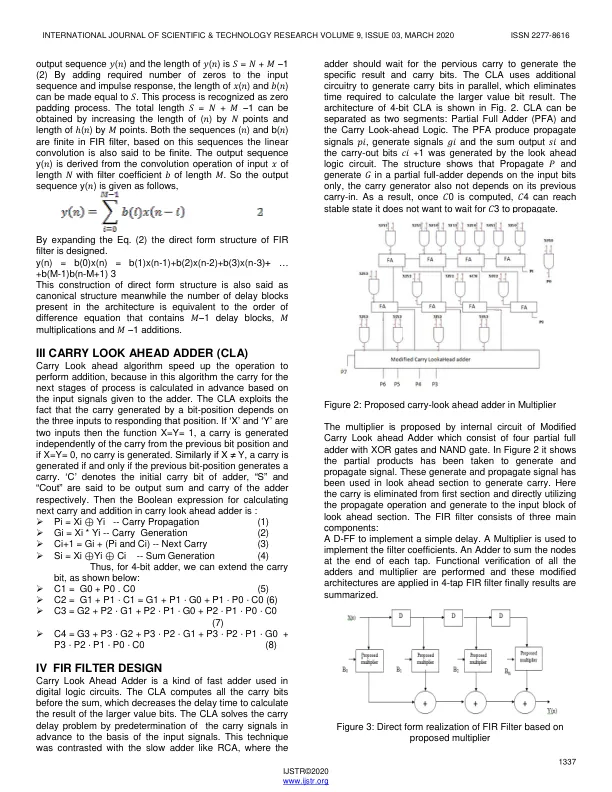

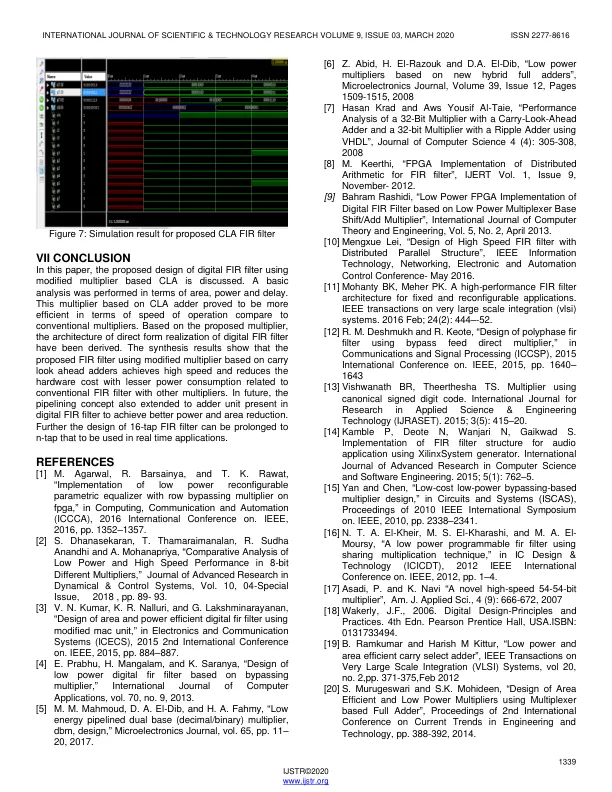

摘要:便携式多媒体设备和通信系统的蓬勃发展,对节省面积和功耗的高速数字信号处理 (DSP) 系统的需求也随之增加。有限脉冲响应 (FIR) 滤波器是设计高效数字信号处理系统的重要组成部分。数字有限脉冲响应 (FIR) 滤波器的使用是 DSP 中的主要模块之一。数字乘法器和加法器是 FIR 滤波器中最关键的算术功能单元,也决定了整个系统的性能。因此,低功耗系统设计已成为主要的性能目标。本文提出了一种使用超前进位加法器和乘法器设计的 FIR 滤波器。其中乘法器由改进型超前进位加法器的内部电路提出。超前进位加法器 (CLA) 用于加法运算,它使用最快的进位生成技术,通过减少修复进位位所需的时间来提高速度,而乘法器则以分层方式执行乘法过程。因此,所提出的方法可以最大限度地降低 FIR 滤波器的有效功率和延迟。初步结果表明,与传统方法相比,使用所提出的乘法器方法的 FIR 滤波器实现了更少的延迟和功率降低。所提出的 FIR 滤波器使用 Verilog 代码进行编程,并使用 Xilinx ISE 14.7 工具进行综合和实现。并使用 Xpower 分析器分析功率。关键词:进位前瞻加法器、FIR 滤波器、乘法器、数字信号处理

采用改进型进位算法对 FIR 滤波器进行分析与设计 ...

主要关键词