机构名称:

¥ 1.0

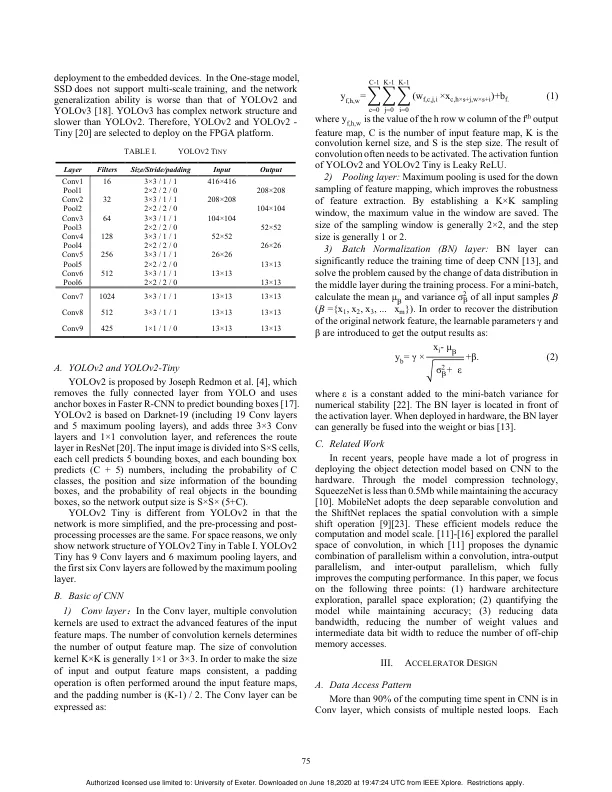

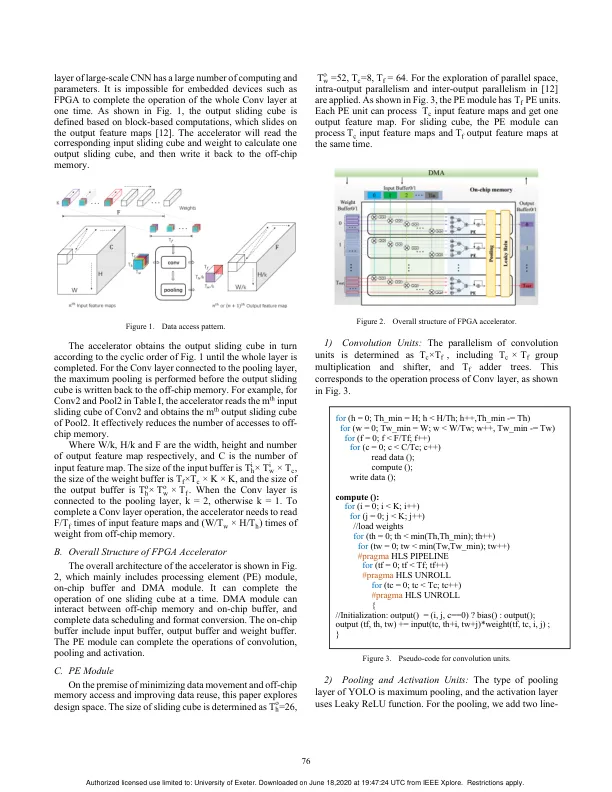

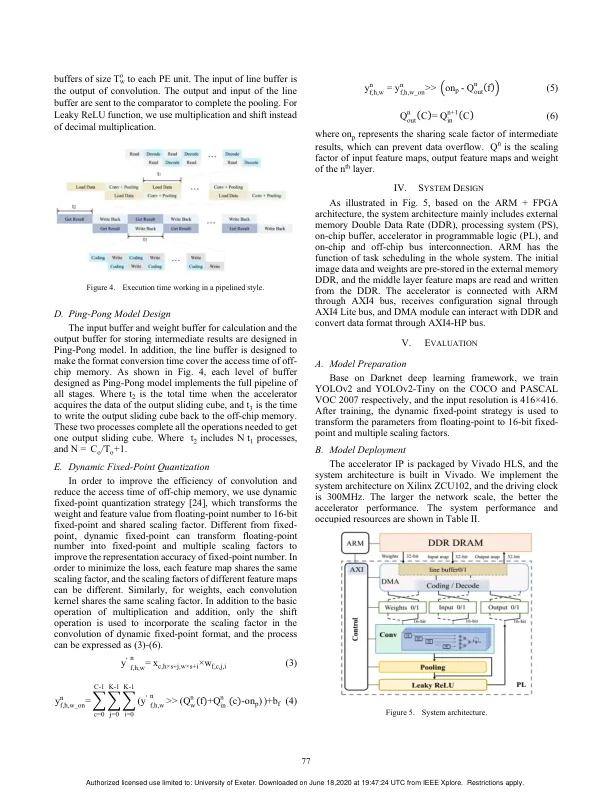

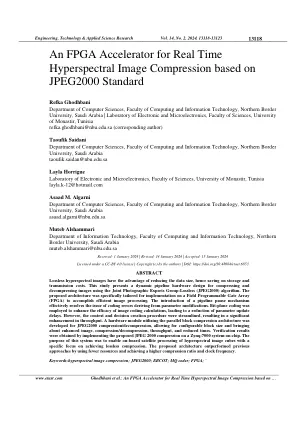

摘要 卷积神经网络(CNN)在图像处理领域得到了广泛的应用,基于CNN的目标检测模型,如YOLO、SSD等,已被证明是众多应用中最先进的。CNN对计算能力和内存带宽要求极高,通常需要部署到专用的硬件平台上。FPGA在可重构性和性能功耗比方面具有很大优势,是部署CNN的合适选择。本文提出了一种基于ARM+FPGA架构的带AXI总线的可重构CNN加速器。该加速器可以接收ARM发送的配置信号,通过分时方式完成不同CNN层推理时的计算。通过结合卷积和池化操作,减少卷积层和池化层的数据移动次数,减少片外内存访问次数。将浮点数转换为16位动态定点格式,提高了计算性能。我们分别在 Xilinx ZCU102 FPGA 上为 COCO 和 VOC 2007 上的 YOLOv2 和 YOLOv2 Tiny 模型实现了所提出的架构,在 300MHz 时钟频率下峰值性能达到 289GOP。

基于 FPGA 的 YOLO 可重构 CNN 加速器

主要关键词