机构名称:

¥ 1.0

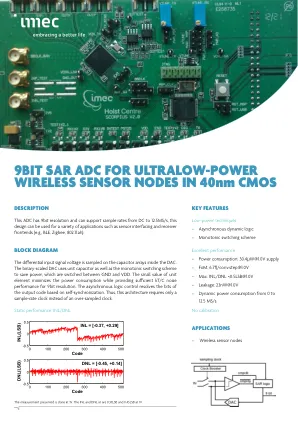

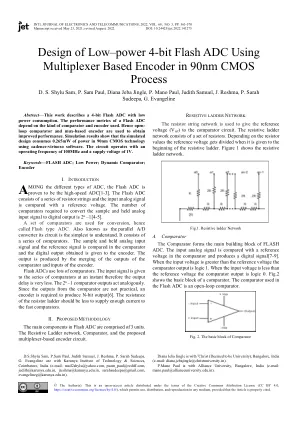

现代仪器系统和数据采集系统需要低到中等分辨率、中速的模数转换器 (ADC)。由于这些系统大多是便携式的,因此 ADC 规范对功率和面积参数有严格的要求。尽管传统的逐次逼近寄存器 (SAR) ADC 因结构简单、模拟模块少而在这些应用中很受欢迎,但它们占用的芯片面积很大。传统 SAR ADC 采用二进制加权电容电荷再分配数模转换器 (DAC) [1,2]。传统电容电荷再分配 DAC 的两个主要限制是转换速度和庞大的电容阵列。较大的 MSB 电容限制了转换速度。这种架构中使用的 DAC 电容阵列变得非常笨重。文献中提出了一些新方法来提高 SAR ADC 的速度 [3,4]。此外,还提出了一些用于 SAR ADC 的面积效率高的 DAC 架构 [5-7]。其中一些 ADC 在性能系数 (FOM) 方面优于其他 ADC,但由于所用 DAC 架构的类型,面积效率 (AE) 参数会降低。[8、9] 中的 SAR ADC 将分辨率可变性融入传统电荷再分配 ADC,以适应需要不同分辨率的多种信号,适用于生物医学信号采集系统等应用。

采用六个单位电容器的、与分辨率无关的全差分 SCI 型 SAR ADC 架构

主要关键词