机构名称:

¥ 1.0

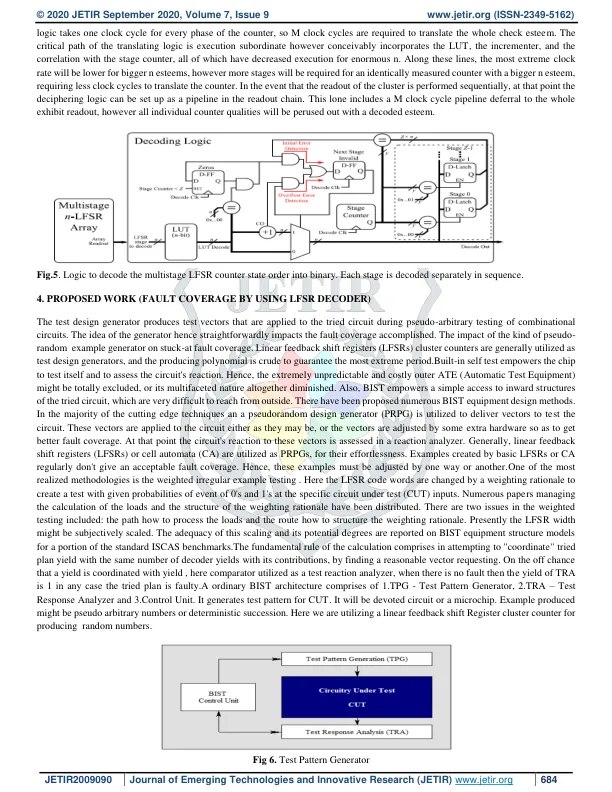

摘要:在这个数字世界中,测试构建的架构已成为一项具有挑战性的任务,而不是构建。测试过程包括高成本和功耗。许多研究都参与了高效测试电路的构建,其中 BIST 是高效测试电路之一。BIST [内置自测试] 提供了一个低功耗、低成本测试电路的平台。BIST 的构建是通过 MULTISTAGE LFSR 解码器电路完成的,该解码器电路通过向构建的架构提供随机和完整的输入序列来为测试电路开辟一条道路。还采用了解码逻辑,使其完美适用于容错架构。据说,由 BIST 和 MULTISTAGE lfsr 组成的路面是查找电路工作故障的有效技术,因此这被称为容错架构,所提出的架构的构建是在 Xilinx ISE 中使用 verilog HDL 语言完成的。索引术语——BIST、MULTISTAGE lfsr、解码逻辑、线性反馈移位寄存器 (LFSR)、基准电路。

采用多级的 BIST 架构设计...

主要关键词