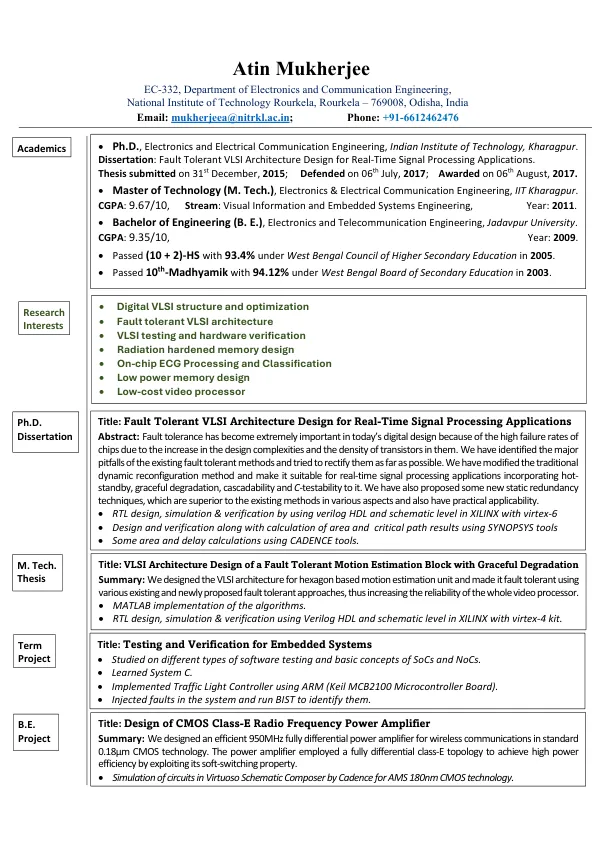

机构名称:

¥ 1.0

标题:用于实时信号处理应用的容错 VLSI 架构设计摘要:由于设计复杂性和晶体管密度的增加导致芯片故障率很高,容错在当今的数字设计中变得极为重要。我们已经确定了现有容错方法的主要缺陷,并尽可能地尝试纠正它们。我们修改了传统的动态重构方法,使其适用于实时信号处理应用,并结合了热备用、优雅降级、级联性和 C 可测试性。我们还提出了一些新的静态冗余技术,这些技术在各个方面都优于现有方法,并且具有实际适用性。• 使用 XILINX 中的 verilog HDL 和原理图级与 virtex-6 进行 RTL 设计、仿真和验证• 使用 SYNOPSYS 工具进行设计和验证以及面积和关键路径结果的计算• 使用 CADENCE 工具进行一些面积和延迟计算。

阿廷·穆克吉

主要关键词