机构名称:

¥ 1.0

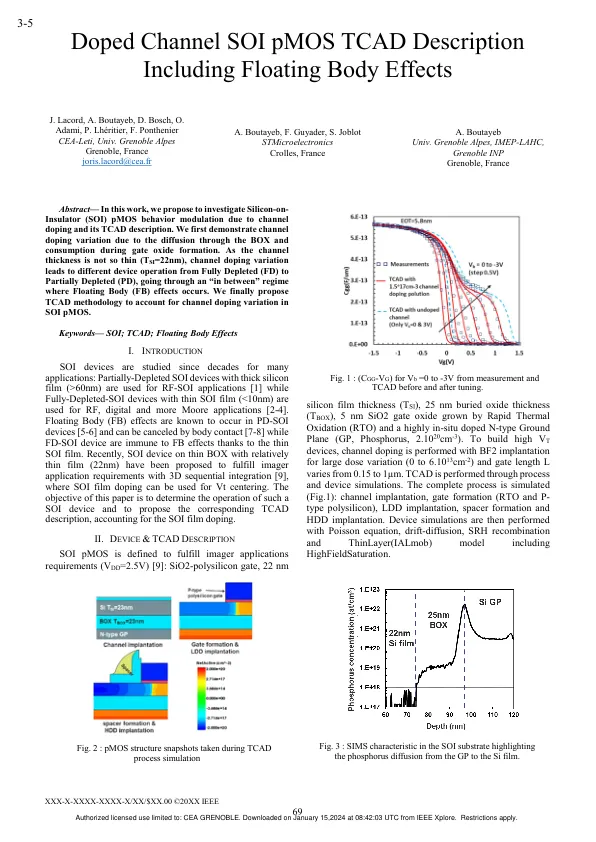

几十年来,人们对 SOI 器件进行了广泛的研究,并将其应用于多种应用:具有厚硅膜(>60nm)的部分耗尽 SOI 器件用于 RF-SOI 应用 [1],而具有薄 SOI 膜(<10nm)的全耗尽 SOI 器件用于 RF、数字和更多 Moore 应用 [2-4]。已知 PD-SOI 器件中会发生浮体 (FB) 效应 [5-6],可以通过体接触消除 [7-8],而 FD-SOI 器件由于具有薄 SOI 膜,因此不受 FB 效应的影响。最近,已经提出了在薄 BOX 上具有相对较薄的薄膜(22nm)的 SOI 器件,以满足 3D 顺序积分的成像器应用要求 [9],其中 SOI 膜掺杂可用于 Vt 居中。本文的目的是确定这种 SOI 器件的操作,并提出相应的 TCAD 描述,考虑 SOI 膜掺杂。

掺杂通道 SOI pMOS TCAD 描述包括浮体效应