机构名称:

¥ 1.0

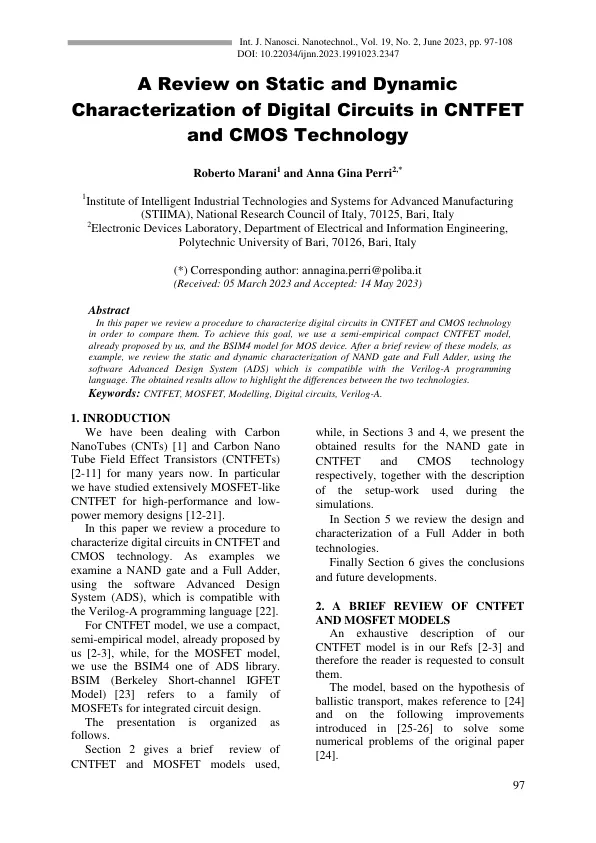

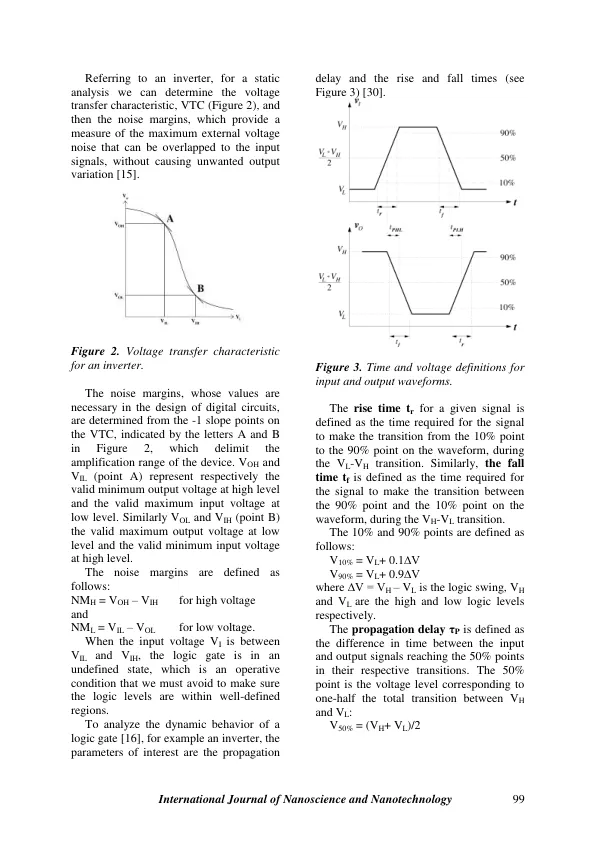

摘要在本文中,我们审查了一种表征CNTFET和CMOS技术中数字电路的程序,以对其进行比较。为了实现此目标,我们使用了我们已经提出的半经验紧凑型CNTFET模型以及MOS设备的BSIM4模型。在对这些模型进行了简要审查之后,我们使用与Verilog-A编程语言兼容的软件高级设计系统(ADS)回顾了NAND门和完整加法器的静态和动态表征。获得的结果允许强调两种技术之间的差异。关键字:CNTFET,MOSFET,建模,数字电路,Verilog-A。1。脱落

cntfet中数字电路的静态和动态表征的综述

主要关键词