机构名称:

¥ 1.0

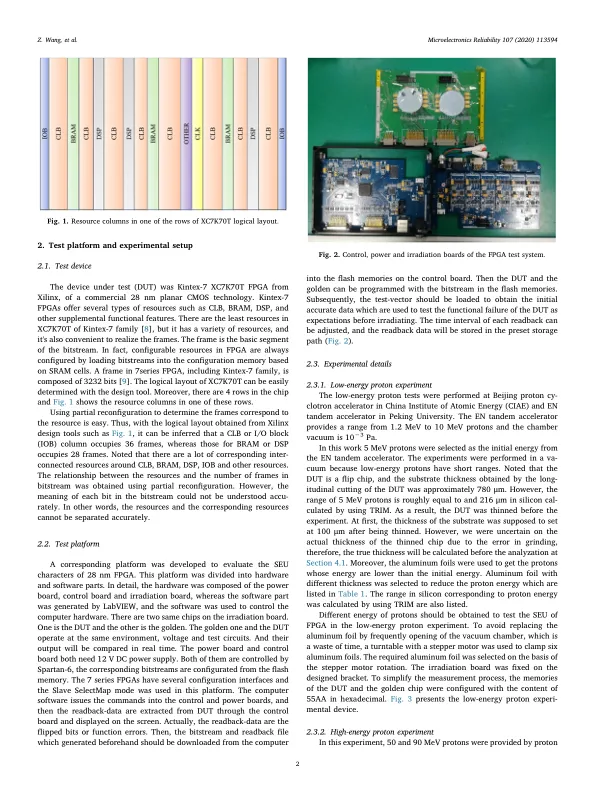

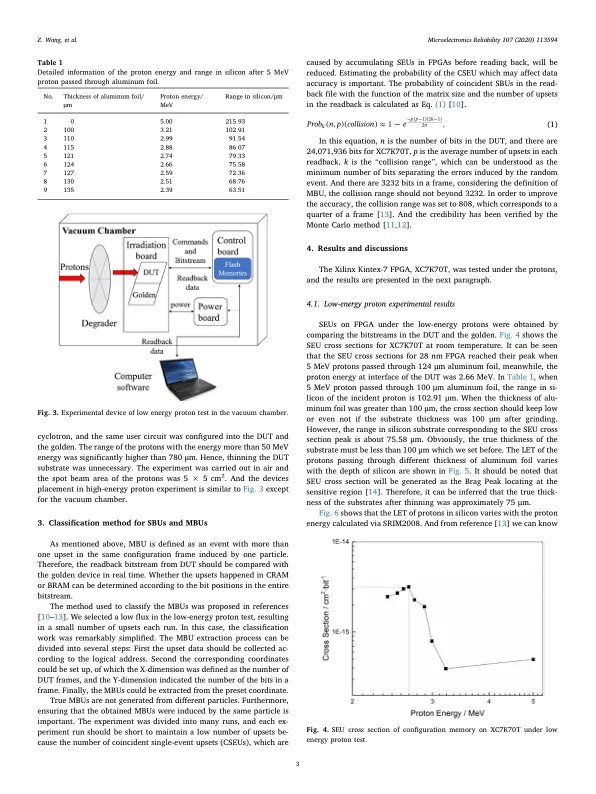

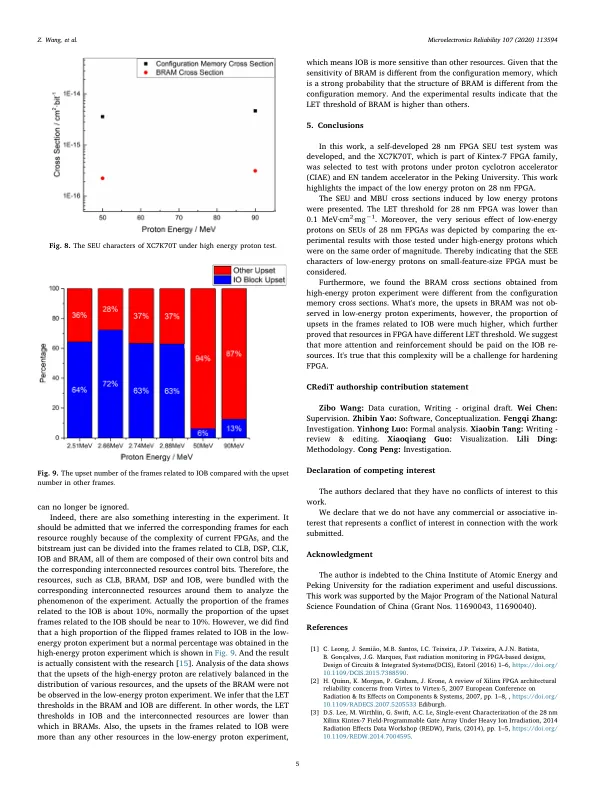

现场可编程栅极阵列(FPGA)由于有能力,低价和高性能等优势,因此受到了各种领域的研究人员的广泛关注。商业FPGA越来越多地用于卫星和其他航天器中。然而,航空航天环境带来了严重的挑战,这是由于带电的颗粒可以轻松在基于SRAM的FPGA的资源中引起单事件效应(参见),例如可配置的逻辑块(CLBS)和块状-RAMS(BRAMS)[1]。因此,在将FPGA的敏感性应用于航空航天工程时,有必要评估它们的敏感性。考虑到单事件不适(SEU)是最常见的现象,因此对FPGA的SEU评估对于采用有针对性的方法来加强设备至关重要。随着技术的缩放,FPGA的特征大小降低到28 nm甚至更小,FPGA中每瓦的资源和性能量得到了极大的改善。seu发生时,当粒子弹动一个单个存储单元时,当粒子在同一帧中的几个位时,在FPGA中发生了多位upsess(MBU)。特征大小的降低的影响很复杂:降低特征大小会导致细胞之间的距离降低。然后粒子可以影响几个细胞,因此,MBU在FPGA上的概率变得更高。此外,还降低了导致浮动的LET阈值,这会导致SEU敏感性增加,这是由于特征尺寸的降低而增加[2]。已经对FPGA进行了大量研究,其特征大小为28 nm甚至更小。最近的工作[3]描述了不同的

质子诱导的单事件对28 nm Kintex-7 FPGA

主要关键词