机构名称:

¥ 1.0

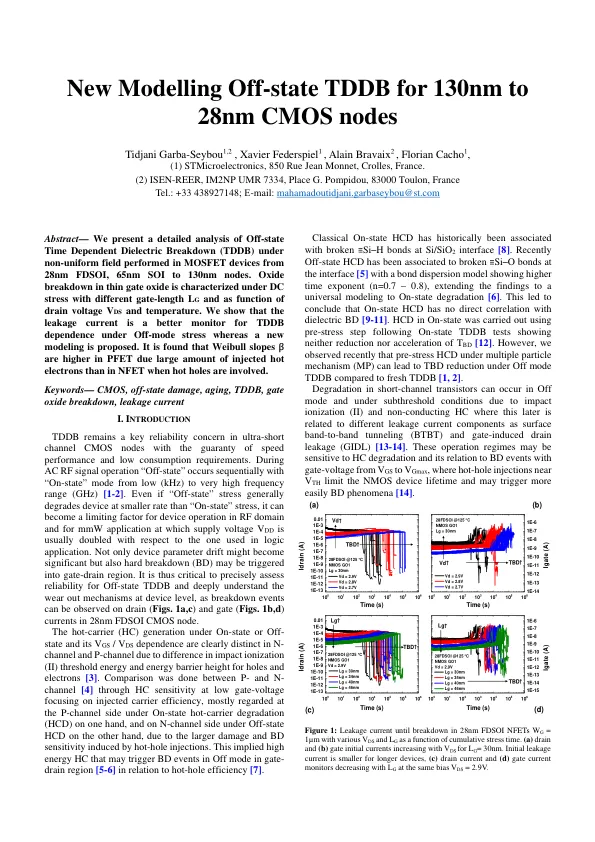

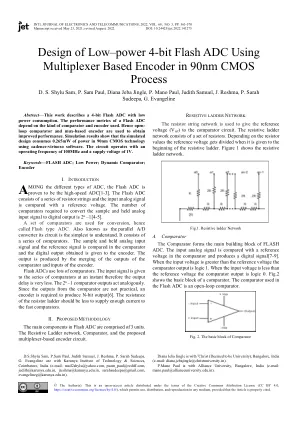

在保证速度性能和低功耗要求的超短通道 CMOS 节点中,TDDB 仍然是一个关键的可靠性问题。在交流射频信号操作期间,“关断状态”与“导通状态”模式依次发生,从低频(kHz)到极高频范围(GHz)[1-2]。即使“关断状态”应力通常以比“导通状态”应力更小的速率降低器件性能,但它可能成为器件在射频域和毫米波应用中运行的限制因素,在毫米波应用中,电源电压 V DD 通常是逻辑应用中使用的电源电压的两倍。不仅器件参数漂移可能变得显著,而且还可能触发栅极-漏极区域的硬击穿(BD)。因此,准确评估关断状态 TDDB 的可靠性并深入了解器件级的磨损机制至关重要,因为可以在 28nm FDSOI CMOS 节点的漏极(图 1a、c)和栅极(图 1b、d)电流上观察到击穿事件。由于空穴和电子的碰撞电离 (II) 阈值能量和能垒高度不同,因此导通或关断状态下热载流子 (HC) 的产生及其 V GS / V DS 依赖性在 N 沟道和 P 沟道中明显不同[3] 。通过低栅极电压下的 HC 敏感性对 P 沟道和 N 沟道进行了比较[4],重点关注注入载流子效率,一方面主要考虑导通状态下的热载流子退化 (HCD) 下的 P 沟道侧,另一方面考虑关断状态下的 N 沟道侧,因为热空穴注入引起的损伤和 BD 敏感性更大。这意味着高能 HC 可能在关断模式下在栅极-漏极区域触发 BD 事件[5-6],与热空穴效率有关[7] 。

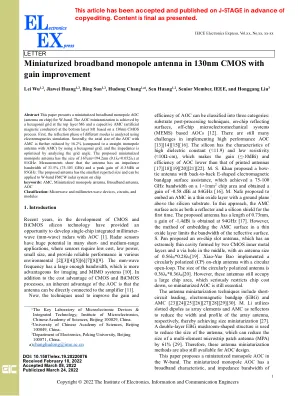

针对 130nm 至 28nm CMOS 节点的新型断态 TDDB 建模

主要关键词