机构名称:

¥ 1.0

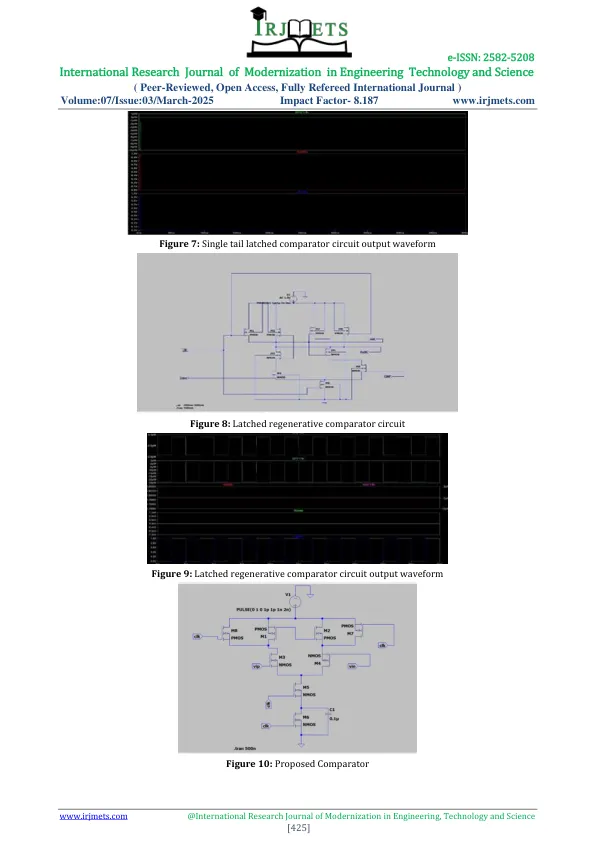

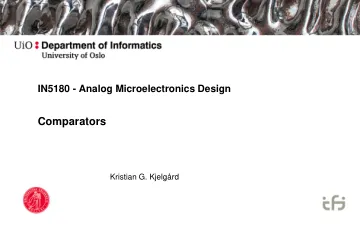

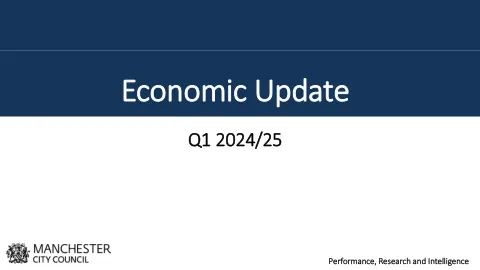

在设计ECG系统时,主要问题之一是功耗,尤其是用于移动和可穿戴设备。本文提出了DTLC适用于使用具有负面偏置的双尾比较器的低端和高端应用程序,以改善使用Mentor图形建模的ECG信号监测系统。使用180nm CMOS技术的EDA工具集成的电路设计,以0.8V的电源提高了电力消耗,而不会下降汽车的性能。参数(包括功耗和功耗产品(PDP))以20 kHz的时钟频率从1.33μW降低到12.5 PW,而PDP降低到27°C时的0.251 AJ,可以改善功耗(PDP)。这些优化使所提出的比较器非常适合低功率,高性能ECG系统,尤其是在便携式和可穿戴的医疗设备中,在这些设备中,作为资源利用和交付的精度是重要因素。设计为公司的数字过渡提供了一个声音平台。心脏信号监测中的类似物到数字转换器(ADC)作为客户对医疗行业中节能声音元素的需求的增长。通过这种方式,功率释放效率得到提高,并且过多的能耗受到限制。根据准确性要求,拟议的比较器可以视为最适合现代心电图应用程序的比较。

低功率双尾动态比较器的ECG

主要关键词