机构名称:

¥ 3.0

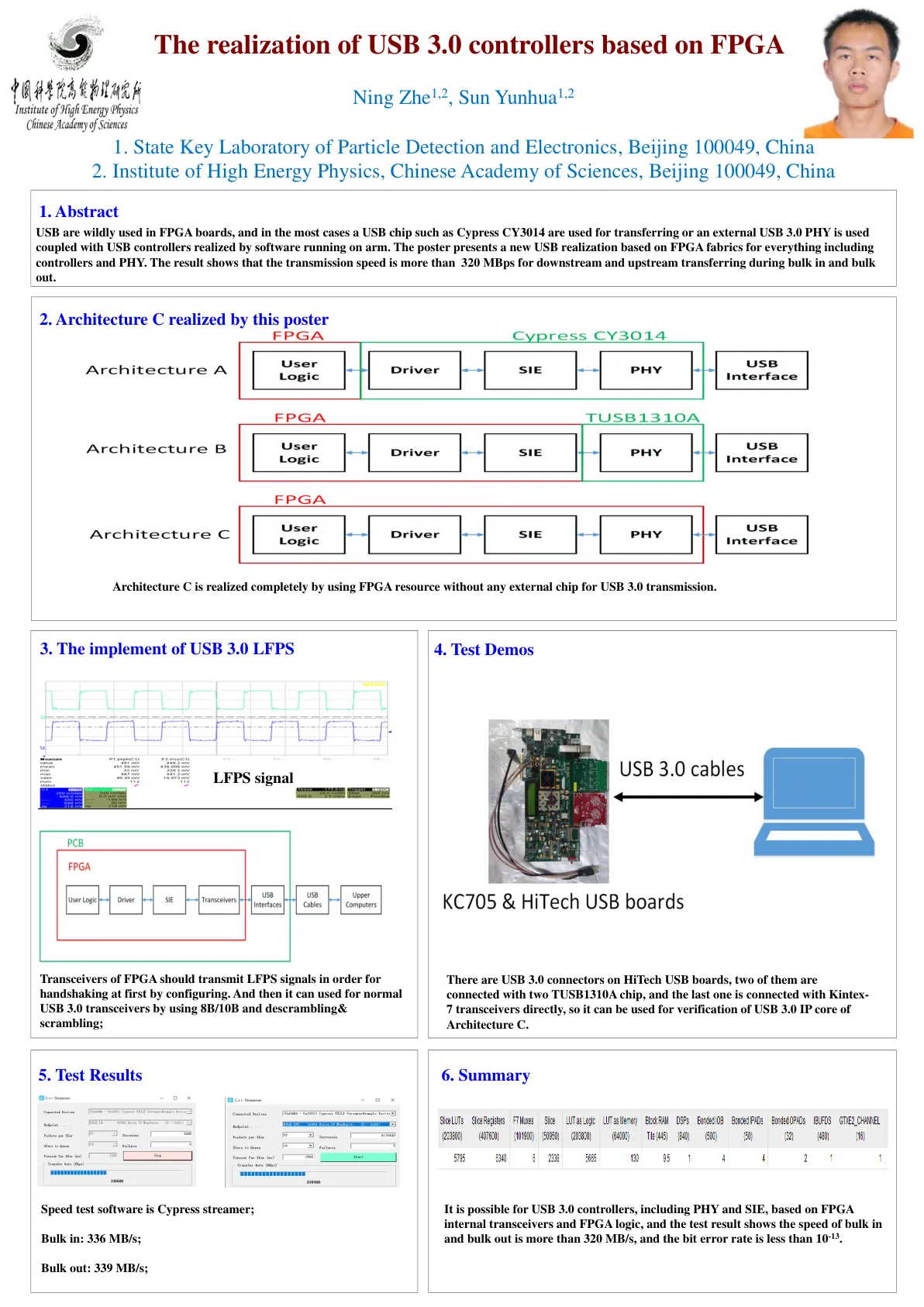

我们展示了如何使用场合可编程的门阵列(FPGA)及其协会的高级合成(HLS)编译器来求解具有不完整市场的异质代理模型,并且汇总了不确定性(Krusell和Smith(Krusell和Smith(1998)))。我们记录了一个单个FPGA传递的加速度与在常规群集中使用69个CPU内核提供的加速度相当。解决模型的1200版的时间从8小时下降到7分钟,说明了结构估计的巨大潜力。我们描述了如何实现多个加速机会(二线,数据级并行性和数据精度),并以为传统的顺序专业人员编写的C/C ++代码的最小修改,然后我们在Amazon Web服务中易于使用FPGA。我们量化了这些加速度的加速和成本。我们的论文是迈向新的,电气工程经济学的第一步,重点是设计经济学的综合加速器,以解决具有挑战性的定量模型。复制代码可在GitHub上获得。

编程FPGA经济学:电气工程经济学简介

主要关键词