机构名称:

¥ 1.0

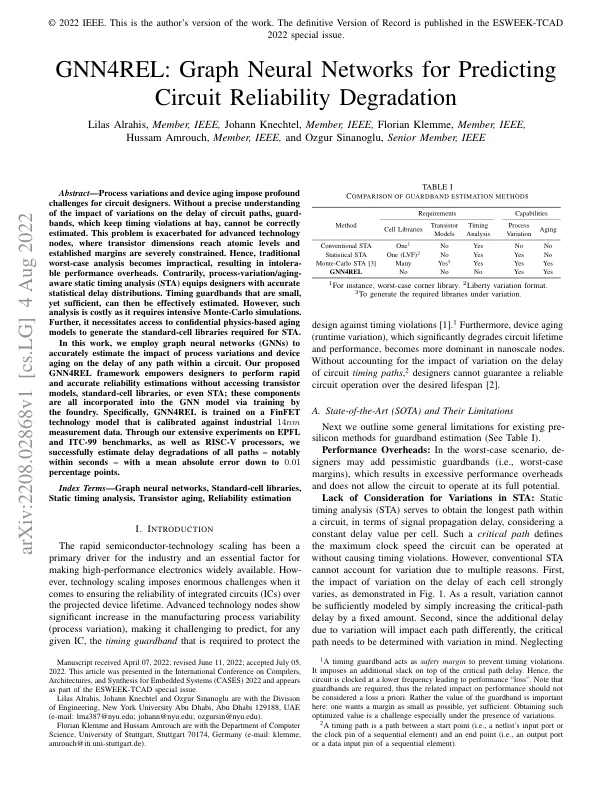

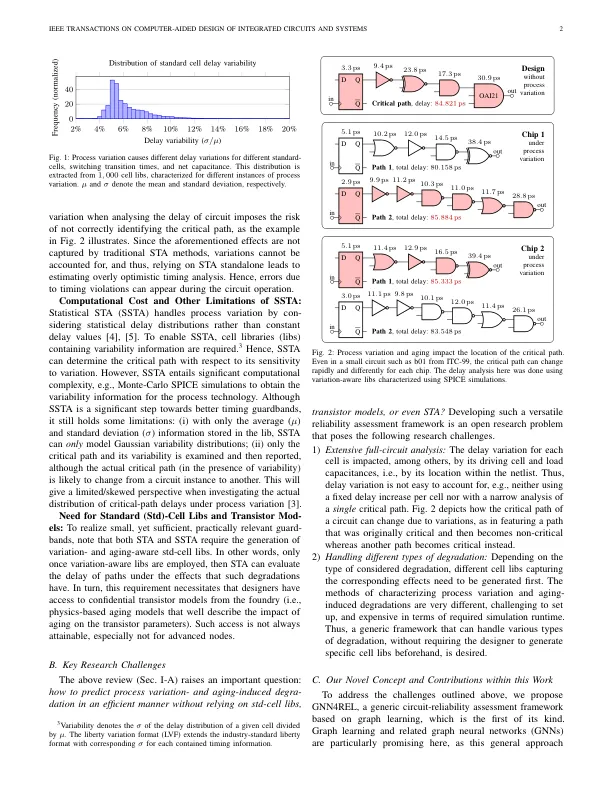

摘要 — 工艺变化和器件老化给电路设计人员带来了巨大的挑战。如果不能准确了解变化对电路路径延迟的影响,就无法正确估计用于防止时序违规的保护带。对于先进技术节点,这个问题更加严重,因为晶体管尺寸达到原子级,既定裕度受到严重限制。因此,传统的最坏情况分析变得不切实际,导致无法容忍的性能开销。相反,工艺变化/老化感知静态时序分析 (STA) 为设计人员提供了准确的统计延迟分布。然后可以有效地估计较小但足够的时序保护带。但是,这种分析成本高昂,因为它需要密集的蒙特卡罗模拟。此外,它需要访问机密的基于物理的老化模型来生成 STA 所需的标准单元库。在这项工作中,我们采用图神经网络 (GNN) 来准确估计工艺变化和器件老化对电路内任何路径延迟的影响。我们提出的 GNN4REL 框架使设计人员能够快速准确地进行可靠性评估,而无需访问晶体管模型、标准单元库甚至 STA;这些组件都通过代工厂的训练整合到 GNN 模型中。具体来说,GNN4REL 是在 FinFET 技术模型上进行训练的,该模型根据工业 14 nm 测量数据进行了校准。通过对 EPFL 和 ITC-99 基准以及 RISC-V 处理器的大量实验,我们成功估计了所有路径的延迟退化(尤其是在几秒内),平均绝对误差低至 0。01 个百分点。

GNN4REL:用于预测电路的图神经网络...