机构名称:

¥ 1.0

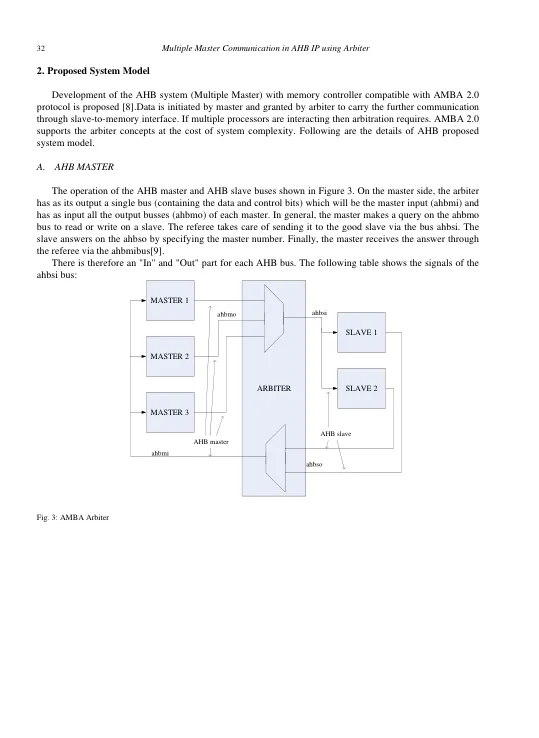

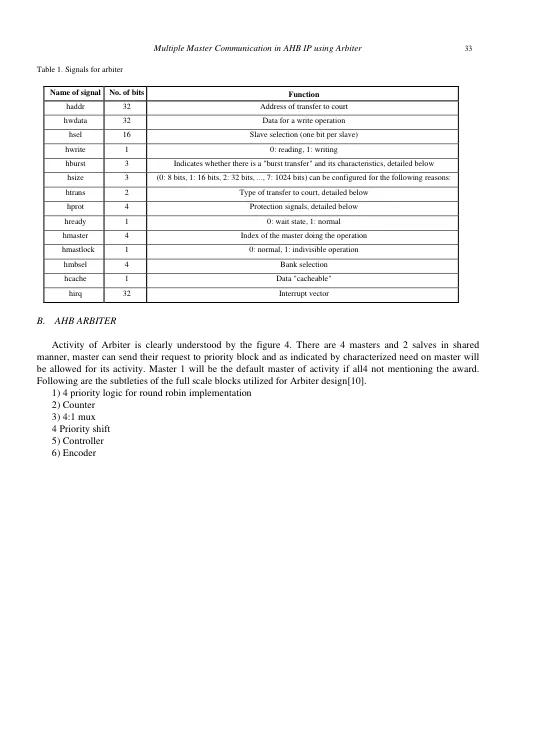

本研究详细阐述了具有四个主控与单个内存系统交互的 AMBA 总线接口,在内存控制器和其他支持外设之间使用仲裁器。使用 VHDL 开发了不同的模块,即 AHB MSTER、AHB SLAVE INTERFACE 和 AHB ARBITER(循环算法)。进一步将 FIFO、RAM 和 ROM 与内存控制器集成。四个 AHB 主控在仲裁器的帮助下启动操作并在单个总线上向内存控制器生成必要的控制信号。与 AHB BUS 系统中多数据通信的先前研究相比,所提出的架构显示了区域高效的管理。该系统模型与 Xilinx XC6vx75t-2ff484 合成,并使用 MODELSIM 进行仿真。索引词:AMBA、AHB Master、AHB Slave、AHB Arbiter、SOC、Xilinx。© 2020 由 MECS Publisher 出版。由现代教育和计算机科学研究协会负责选择和/或同行评审

使用仲裁器在 AHB IP 中进行多主通信

主要关键词