机构名称:

¥ 1.0

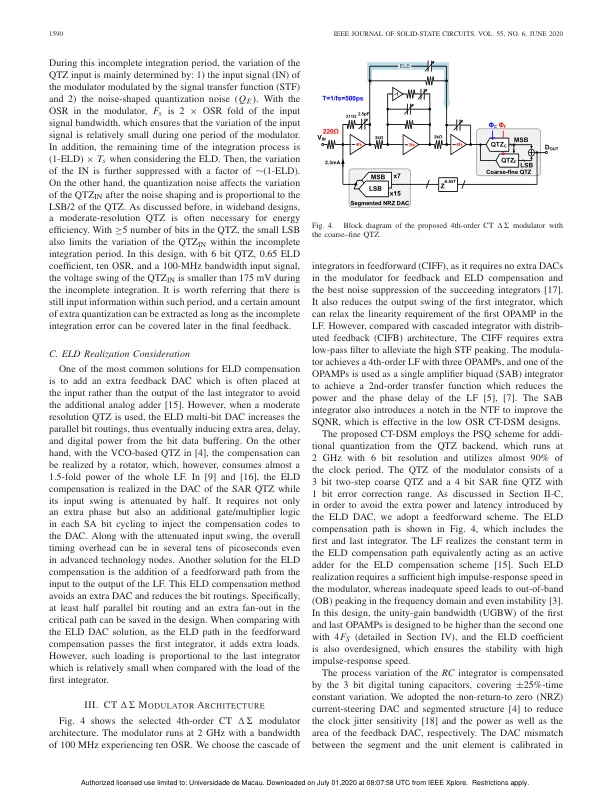

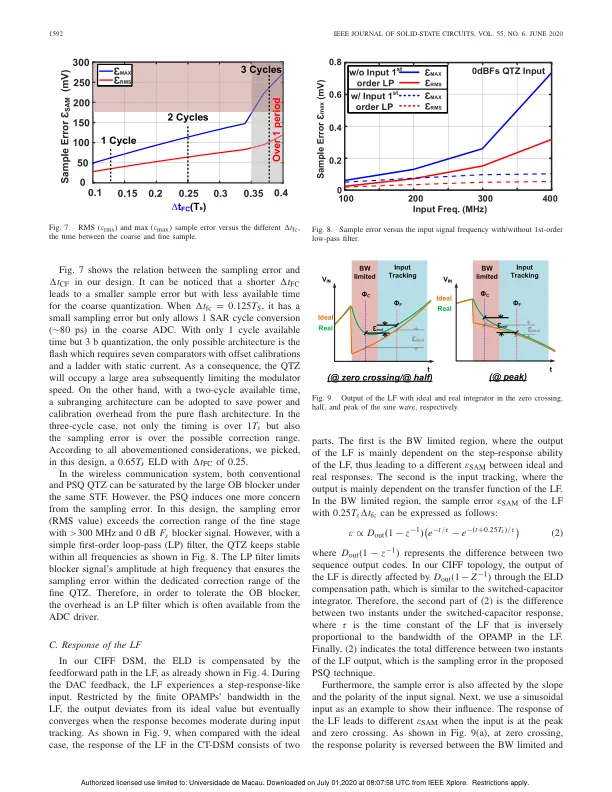

摘要 — 本文介绍了一种 28 nm CMOS 工艺的四阶 100 MHz 带宽连续时间 (CT) delta-sigma 调制器。介绍了一种初步采样和量化 (PSQ) 技术,该技术几乎可以充分利用量化时钟周期,从而在 0.65 过量环路延迟 (ELD) 系数下延长后端量化器 (QTZ) 的可用转换时间。使用 PSQ,后端 QTZ 的采样和量化分为粗采样和细采样两个步骤,类似于子范围架构以节省功耗。QTZ 以 2 GHz 运行,仅需 1.4 mW 功率即可实现 7 位 (1 b 纠错)。通过在前馈 (CIFF) 拓扑中的积分器级联中添加前馈 ELD 补偿路径,此设计中只需要一个数模转换器 (DAC)。该调制器的信号带宽为 100 MHz,信噪比 (SNDR) 为 72.6 dB,功耗仅为 16.3 mW(1.1 和 1.5 V 电源供电)。原型的动态范围为 76.3 dB,Schreier FoM 为 174.2 dB,有效面积为 0.019 mm 2 。

采用 ... 的 100 MHz BW 72.6 dB-SNDR CT 调制器

主要关键词