机构名称:

¥ 1.0

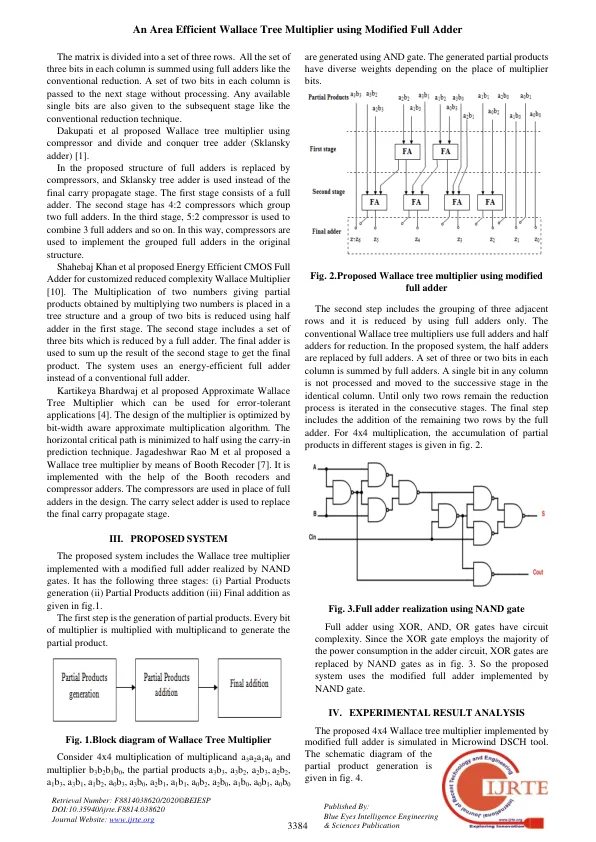

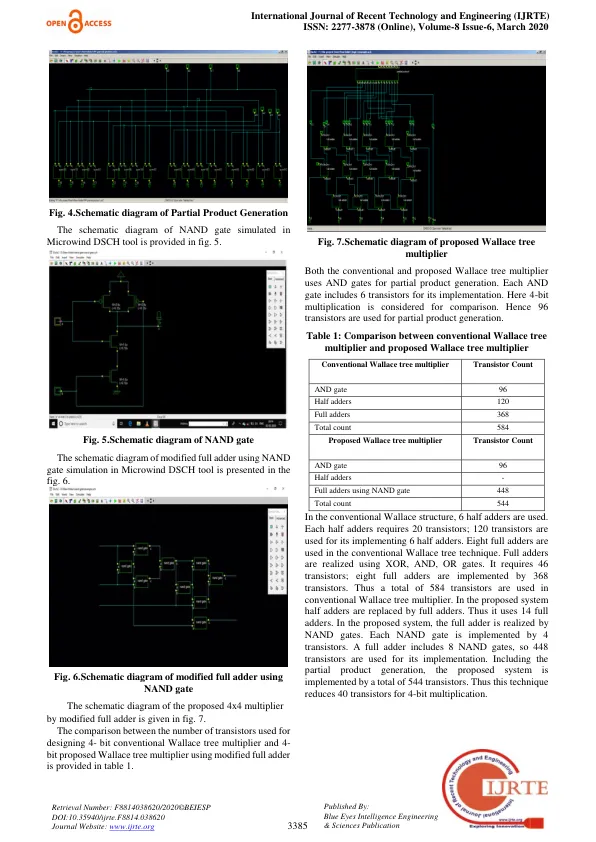

摘要:乘法器在数字信号处理应用和专用集成电路中起着重要作用。华莱士树乘法器提供了一种具有面积高效策略的高速乘法过程。它使用全加器和半加器在硬件中实现。加法器的优化可以进一步提高乘法器的性能。提出了一种使用 NAND 门改进全加器的华莱士树乘法器,以实现减小的硅片面积、高速度和低功耗。用 NAND 门实现的改进全加器取代由 XOR、AND、OR 门实现的传统全加器。提出的华莱士树乘法器包含 544 个晶体管,而传统的华莱士树乘法器有 584 个晶体管用于 4 位乘法。

使用改进的面积高效华莱士树乘法器...