机构名称:

¥ 1.0

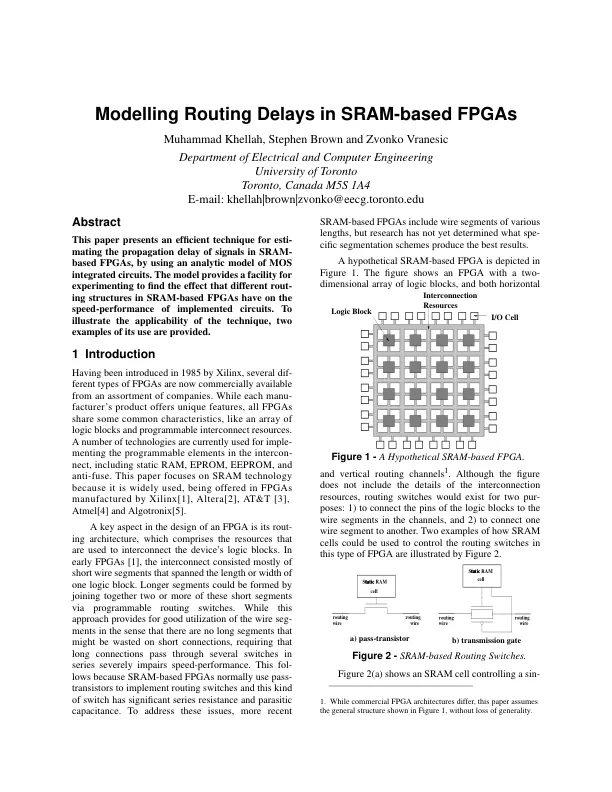

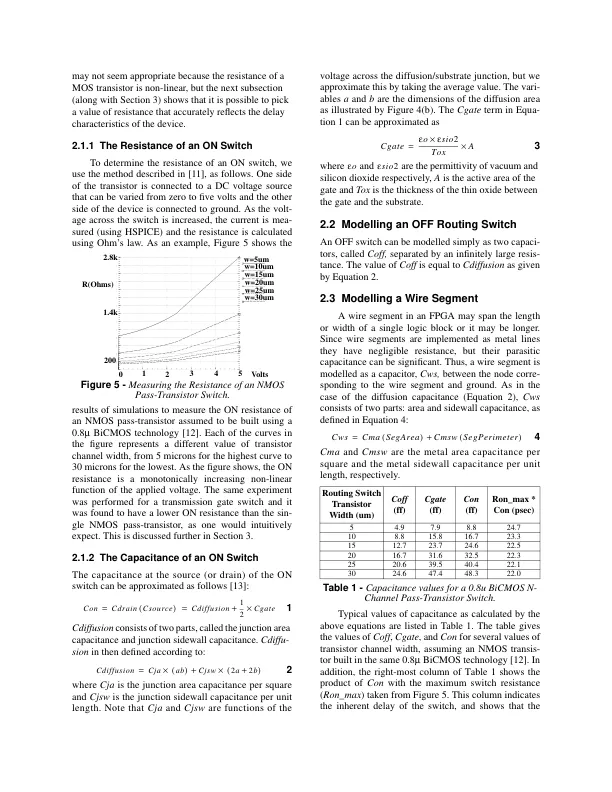

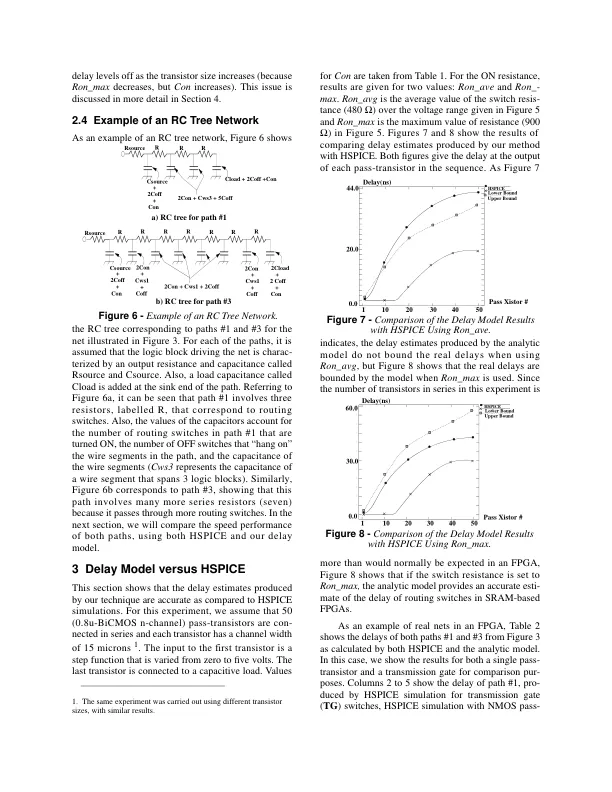

FPGA 设计的一个关键方面是其布线架构,它包括用于互连器件逻辑块的资源。在早期的 FPGA [1] 中,互连主要由跨越一个逻辑块长度或宽度的短线段组成。可以通过可编程布线开关将两个或多个短线段连接在一起来形成较长的线段。虽然这种方法可以很好地利用线段,因为没有可能浪费在短连接上的长线段,但要求长连接通过多个串联开关会严重影响速度性能。这是因为基于 SRAM 的 FPGA 通常使用传输晶体管来实现布线开关,而这种开关具有很大的串联电阻和寄生电容。为了解决这些问题,最近提出了一种用于互连的布线开关,用于将两个或多个短线段连接在一起的布线开关。

基于 SRAM 的 FPGA 中的布线延迟建模