机构名称:

¥ 1.0

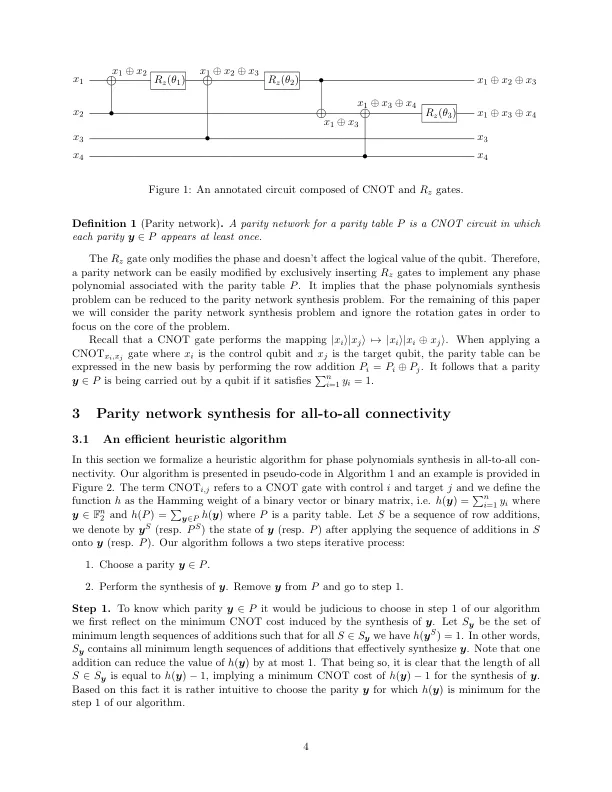

量子电路优化对于提高量子计算的实用性和效率至关重要。特别是,为了满足量子电路急需的紧凑性,可逆电路的合成正在被深入研究。由于 T 门具有较高的容错实现成本 [1],因此人们投入了大量工作来最小化 T 数量 [2–9] 和 T 深度 [10–13]。相比之下,CNOT 门的实现成本较低,因为它是 Clifferd 群的一部分 [14]。尽管如此,基于 T 门的度量的使用有局限性,事实证明,电路中 CNOT 门的数量是一个不容忽视的度量,因为它会对电路的实现成本产生重大影响 [15]。除此之外,噪声中尺度量子 (NISQ) 时代的量子计算机 [16] 具有架构限制。具体而言,这些计算机中的量子比特并非以全对全的方式连接。这意味着具有 2 的元数的逻辑门(例如 CNOT 门)只能应用于某些量子比特对之间。因此,使电路符合给定架构不可避免地会导致 CNOT 计数增加 [17]。处理架构约束的一种常见方法是插入 SWAP 门来路由逻辑量子比特 [18–21]。另一种方法是执行架构感知合成 [22],这种方法通常会产生具有低得多的 CNOT 计数的电路,同时满足架构约束。这种方法通常应用于可以用高级构造(例如线性可逆函数)表示的电路子集。然后可以将这些电路组合在一起以形成完整的架构兼容量子电路 [23, 24]。此编译方案中的一个重要构建块是合成仅由 CNOT 和 RZ 门组成的电路。这些电路可以用称为相位多项式的高级构造来表示。在这项工作中,我们解决了相位多项式合成问题,并针对受限和完全连接的情况提出了有效的算法。

NISQ 架构及其他架构的相位多项式合成算法

主要关键词