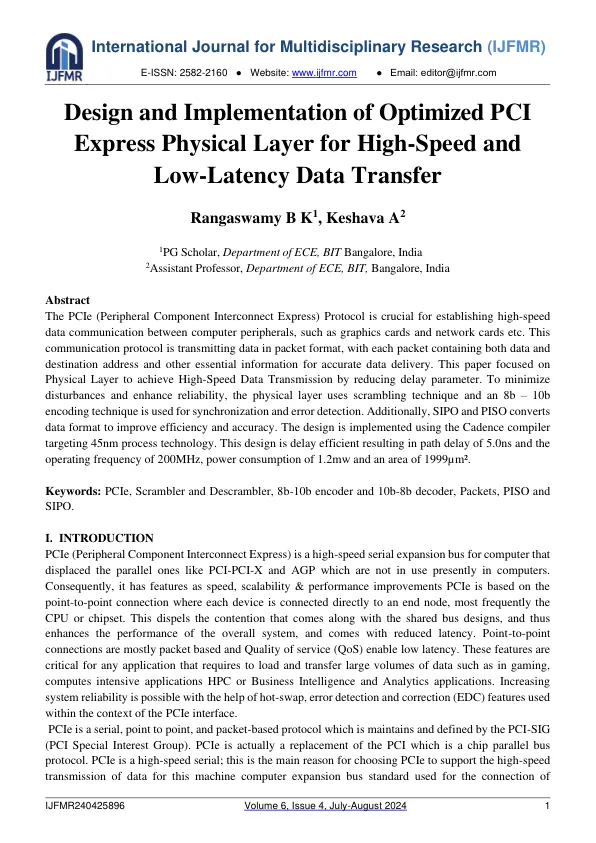

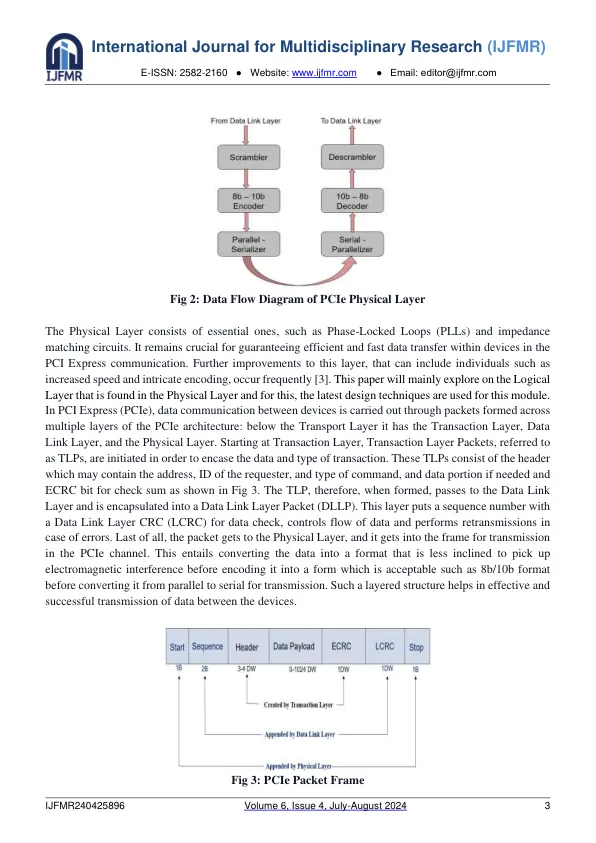

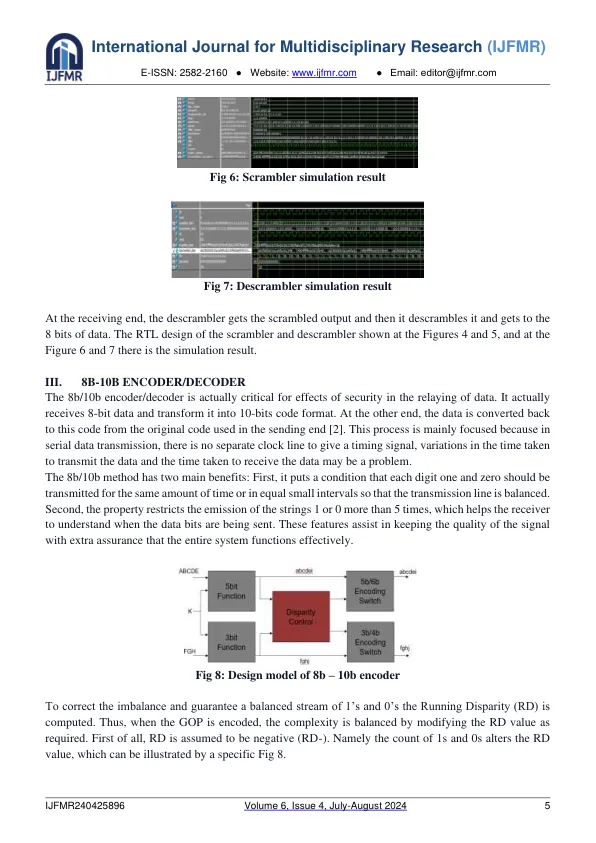

1 研究生学者,印度班加罗尔 BIT 电子与计算机工程系 2 助理教授,印度班加罗尔 BIT 电子与计算机工程系 摘要 PCIe(外围组件互连快捷)协议对于在计算机外围设备(如显卡和网卡等)之间建立高速数据通信至关重要。此通信协议以数据包格式传输数据,每个数据包包含数据和目标地址以及其他准确传输数据的基本信息。本文重点研究物理层通过降低延迟参数实现高速数据传输。为了最大限度地减少干扰并提高可靠性,物理层使用加扰技术,并使用 8b – 10b 编码技术进行同步和错误检测。此外,SIPO 和 PISO 转换数据格式以提高效率和准确性。该设计使用针对 45nm 工艺技术的 Cadence 编译器实现。该设计具有延迟效率,路径延迟为 5.0ns,工作频率为 200MHz,功耗为 1.2mw,面积为 1999µm²。关键词:PCIe、加扰器和解扰器、8b-10b 编码器和 10b-8b 解码器、数据包、PISO 和 SIPO。I. 简介 PCIe(外围组件互连快速)是一种用于计算机的高速串行扩展总线,它取代了目前计算机中未使用的并行总线,如 PCI-PCI-X 和 AGP。因此,它具有速度、可扩展性和性能改进等特点 PCIe 基于点对点连接,其中每个设备直接连接到终端节点,最常见的是 CPU 或芯片组。这消除了共享总线设计带来的争用,从而提高了整个系统的性能,并降低了延迟。点对点连接大多基于数据包,服务质量 (QoS) 可实现低延迟。这些功能对于需要加载和传输大量数据的任何应用程序都至关重要,例如游戏、计算密集型应用程序 HPC 或商业智能和分析应用程序。借助 PCIe 接口中使用的热插拔、错误检测和纠正 (EDC) 功能,可以提高系统可靠性。PCIe 是一种串行、点对点和基于数据包的协议,由 PCI-SIG(PCI 特别兴趣小组)维护和定义。PCIe 实际上是 PCI 的替代品,PCI 是一种芯片并行总线协议。PCIe 是一种高速串行;这是选择 PCIe 来支持此机器高速数据传输的主要原因,用于连接的计算机扩展总线标准

优化 PCI Express 的设计与实现...

主要关键词