机构名称:

¥ 1.0

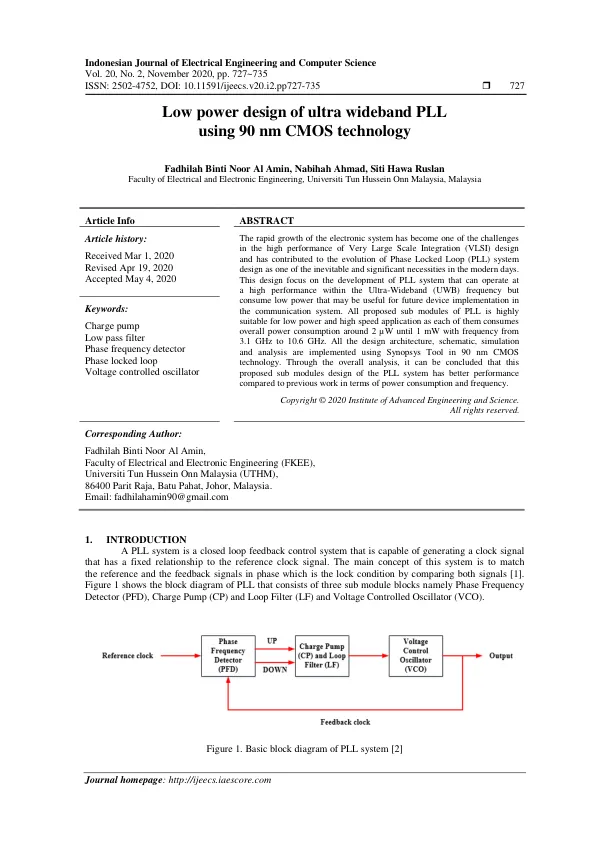

电子系统的快速增长已成为非常大规模集成(VLSI)设计的高性能的挑战之一,并为相位锁定环(PLL)系统设计的发展做出了贡献,它是现代不可避免的重要必需品之一。这种设计集中于可以在超宽带(UWB)频率内以高性能运行的PLL系统的开发,但消耗了低功率,这可能对通信系统中的将来的设备实现有用。PLL的所有提议的子模块都非常适合低功率和高速应用,因为它们每个人都消耗了2 µW左右的总体功耗,直到1 MW,频率从3.1 GHz到10.6 GHz。使用90 nm CMOS技术中的Synopsys工具实现了所有设计架构,示意图,仿真和分析。通过整体分析,可以得出结论,在功耗和频率方面,与以前的工作相比,PLL系统的拟议子模块设计具有更好的性能。

使用90 nm的超宽带PLL的低功率设计...

主要关键词