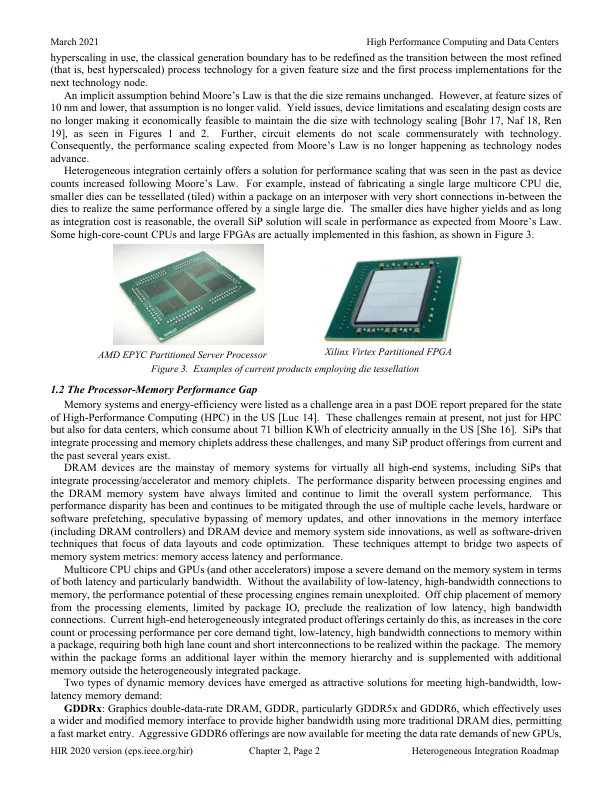

1。简介:针对高性能计算(HPC)和数据中心市场的异质整合半导体设备的需求始终代表了设备和过程技术中普遍存在的最先进。这些细分市场的需求通常要求达到最高的处理率,最高的沟通速率(低潜伏期和高带宽,通常是同时同时同时使用这些)和最高的能力,并且对包装的极端要求,以满足互连需求和更高的功率散失。这是一种趋势,它很可能会随着HPC系统和数据中心的各种应用而持续,近年来已经出现了。术语chiplet已用于描述与包装中其他此类模具(或chiplets)集成的模具。替代术语dielet也被同义用作chiplet。在本章中,这些术语可互换使用。顺便说一句,值得注意的是,chiplet一词严格意味着不一定独立的功能性芯片的一部分。在使用该术语的方式中,chiplet可以是一个完全运行的模具,例如HBM堆栈或多核CPU。在当前用途时,chiplet一词用于指代术语的严格含义,指代零件或整个功能性芯片。本章合理化了对实现HPC和数据中心市场的系统集成系统集成的明确需求,并确定了潜在的解决方案以及在实现这些SIP时遇到的潜在解决方案以及短期,中期和长期挑战。尽管与过去一样,处理器 - 内存性能差距仍然是整个系统体系结构的关键驱动力,但推动HPC和数据中心市场中异质集成需求的新因素已经出现。这些包括技术局限性,新的和新兴的应用程序以及缩放需求,以克服功率耗散,功率输送和包装IO约束。这些需求及其含义将在下面检查。1.1过去的尺寸限制,技术节点(功能尺寸)一直是特定一代主流CMOS技术的代表,并且在引入后的18至24个月内,新技术超过了最新的技术。近年来,作为特征大小缩减的节点实际上涵盖了几个连续的技术一代,其特征是通过过程优化和电路重新设计在节点内实现的电路元素的缩小尺寸。因此,一个节点已经开始持续数年,但实际上使缩小电路元素的扩展能够继续通过这些创新(称为“超级标准” [BOHR 17]),以相对固定的特征大小。近年来已经成立的共识是使用技术缩放度量指标,该指标代表某些基本电路元素(例如Nand Gates或Scan Flip-Flops [BOHR 17]或其他特定于供应商[LU 17])的技术规模。使用

第2章:高性能计算

主要关键词