机构名称:

¥ 1.0

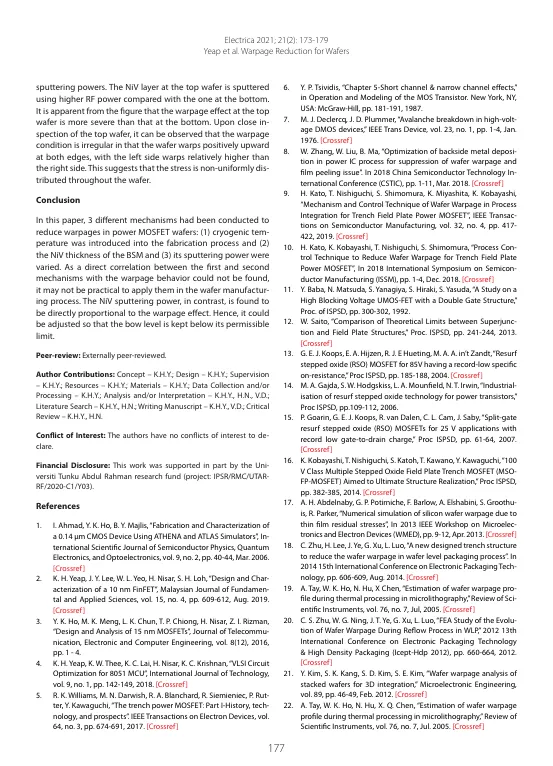

Wafer Warpage是半导体制造商面临的基线问题,实际上,在与制造功率金属氧化物半导体磁场效应晶体管(MOSFET)的制造的人中尤为明显。这是因为垂直MOSFET与传统的外侧对应物相比会经历更大的经线效应。wafers超过其临界价值的瓦金(Wafers)在自动处理过程中无法通过吸尘器吸附来削减其临界价值;晶圆上制造的设备也面临可靠性问题。本文介绍了用于减少电源MOSFET晶体经纪的各种机制的分析。通过改变背面金属化(BSM)厚度,膜沉积的溅射功率和晶片温度(即将低温条件引入过程中)来检查扭曲行为。结果表明,当前端制造过程完成后,BSM厚度和晶圆的温度都与晶圆经膜的相关性明显相关。晶圆弓水平与溅射功率的大小直接成比例。当溅射功率降低时,诱发残留应力较小以变形晶片结构。因此,可以调整溅射功率,以确保扭曲效应保持在其临界值以下。关键字:经形,功率MOSFET,残余压力,背面金属化,溅射功率,低温温度

功率MOSFET WAFERS的降压 - 电气

主要关键词