机构名称:

¥ 1.0

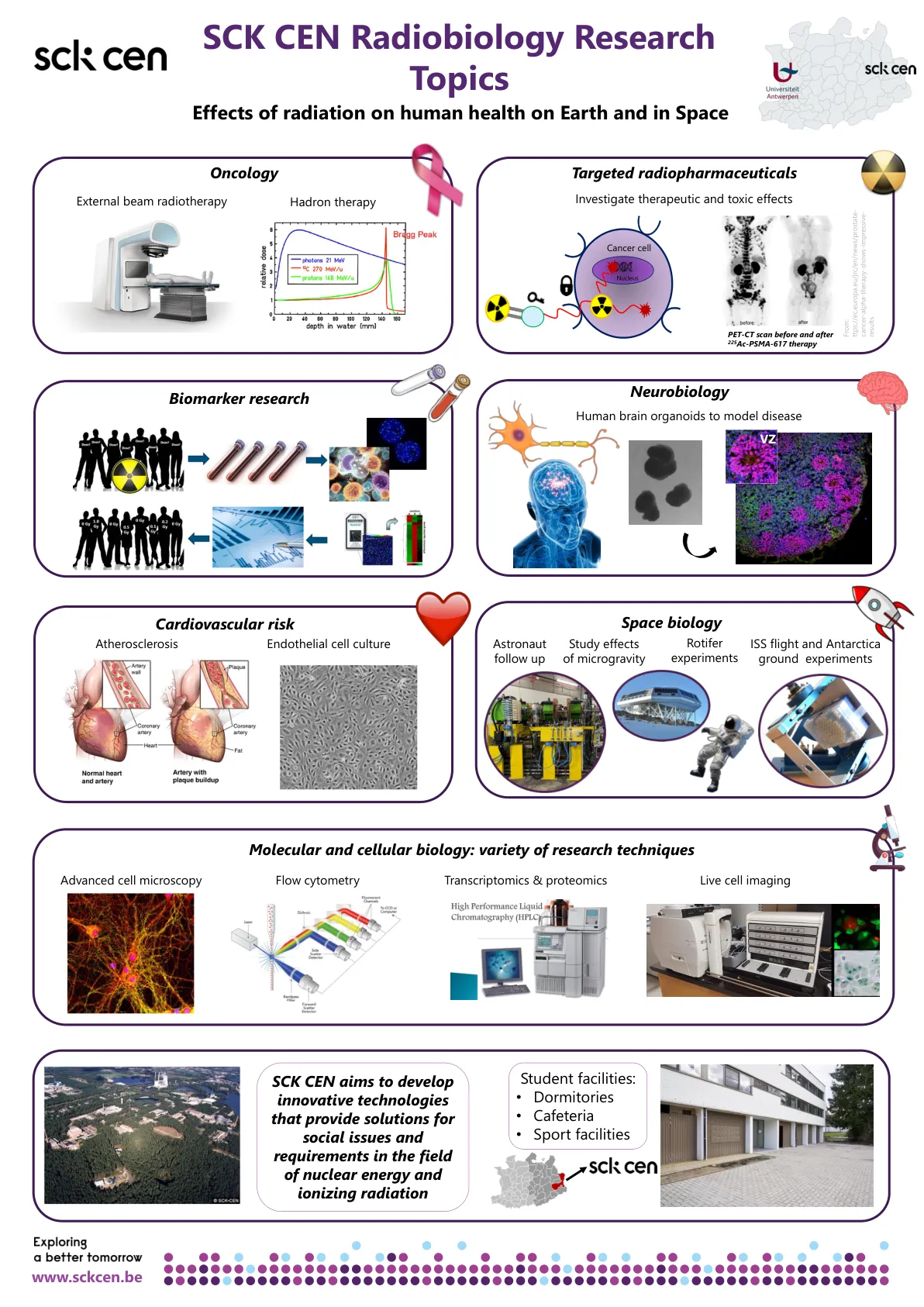

密码算法在社会多个领域的日常实践(如电子支付、数据交换)中发挥着关键作用,包括金融、医疗保健和政府机构。与软件解决方案相比,在低级硬件设计中实现密码算法具有一组独特的约束(如硬件和计算资源)和需要优化的额外性能指标(如功耗)。考虑到这些限制,人们在 ASIC [1,2] 和 FPGA [3,4] 中彻底研究了不同的轻量级但强大的优化技术。尽管基于 SRAM 的 FPGA 上的密码实现功能多样且具有成本效益,但它极易受到辐射引起的软错误的影响,因此,对可靠解决方案的研究备受关注 [5] 。在这方面,人们已经使用了不同的缓解技术和实施方案来减少软错误对 FPGA 上实现的密码解决方案的影响 [6] 。例如,Bertoni 等人 [5] 将冗余技术与错误检测码结合使用来检测单比特故障。 Banu 等人 [7] 描述了一种基于汉明纠错码的 AES 容错模型。同样,Wu 等人 [8] 提出了一种低成本的 AES 并发错误检测方法

辐射引起的软错误对嵌入式加密算法的影响

主要关键词