机构名称:

¥ 1.0

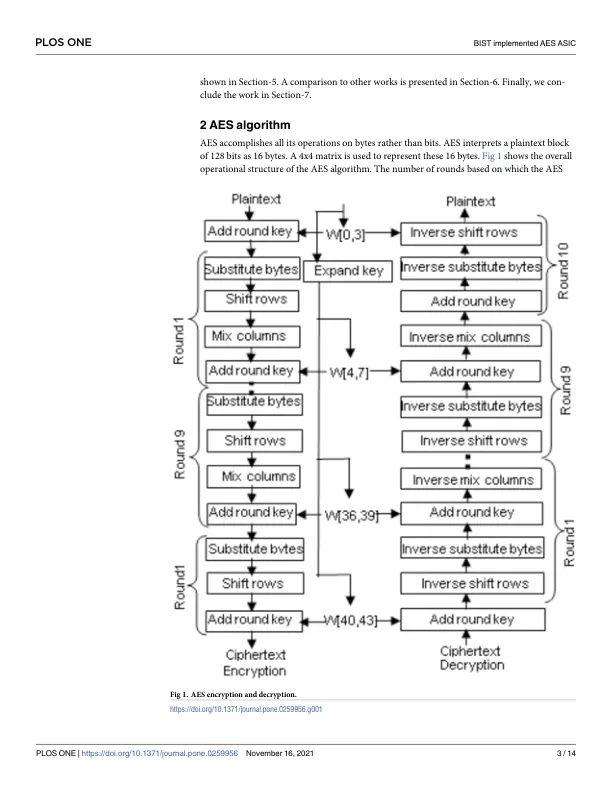

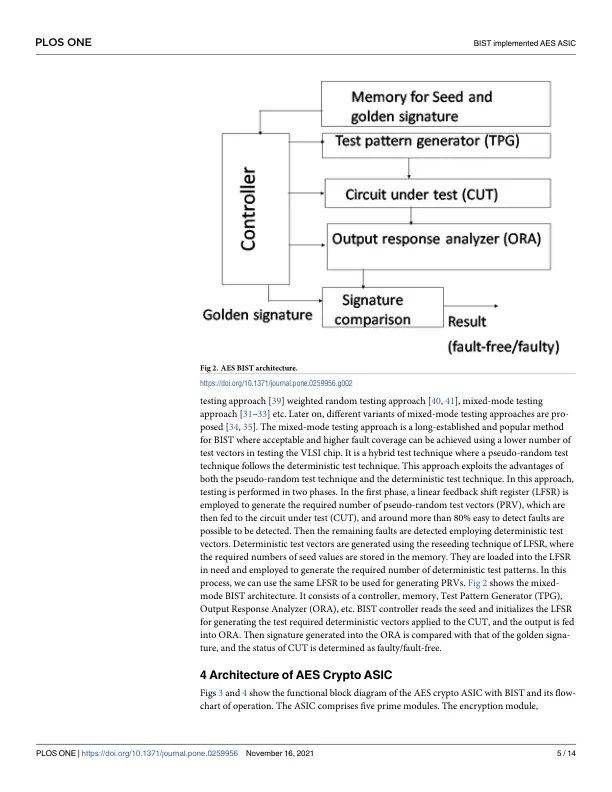

本文介绍了一种基于内建自测试 (BIST) 的高级加密标准 (AES) 加密处理器专用集成电路 (ASIC) 的设计。AES 已被证明是美国政府宣布的最强大的对称加密算法,其性能优于所有其他现有加密算法。其硬件实现比软件实现提供更高的速度和物理安全性。由于这个原因,文献中已经提出了许多 AES 加密处理器 ASIC,但复杂 AES 芯片中的可测试性问题尚未得到解决。本研究为实现混合模式 BIST 技术的 AES 加密处理器 ASIC 引入了一种解决方案,该技术是伪随机和确定性技术的混合。BIST 实现的 ASIC 是使用 IEEE 行业标准硬件描述语言 (HDL) 设计的。它已使用电子设计自动化 (EDA) 工具进行了模拟,并使用美国政府国家标准与技术研究所 (NIST) 的输入输出数据进行了验证和确认。模拟结果表明,该设计在 ASIC 的不同操作模式下按预期功能运行。将当前的研究与其他研究人员的研究进行了比较,结果表明它在 BIST 实现到 ASIC 芯片方面是独一无二的。

设计基于 BIST 的 AES 加密处理器 ASIC

主要关键词