机构名称:

¥ 1.0

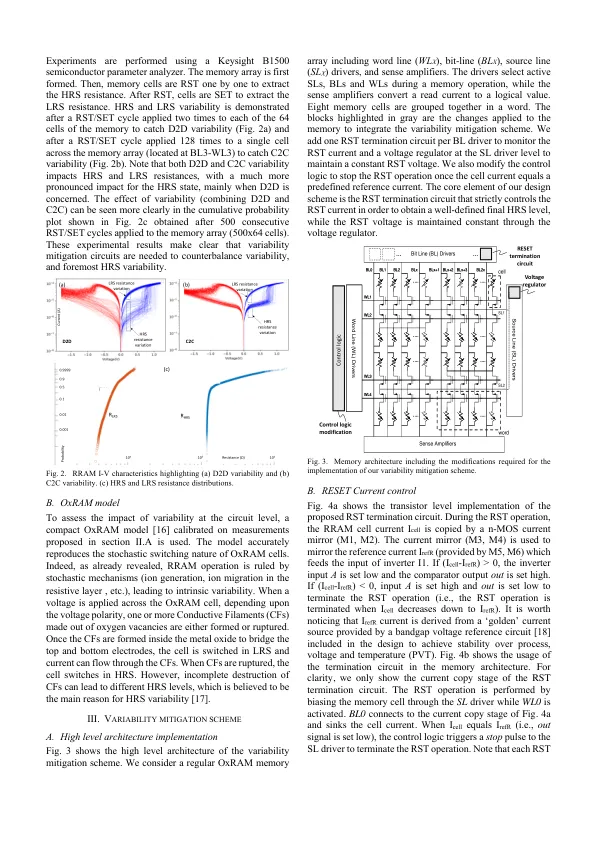

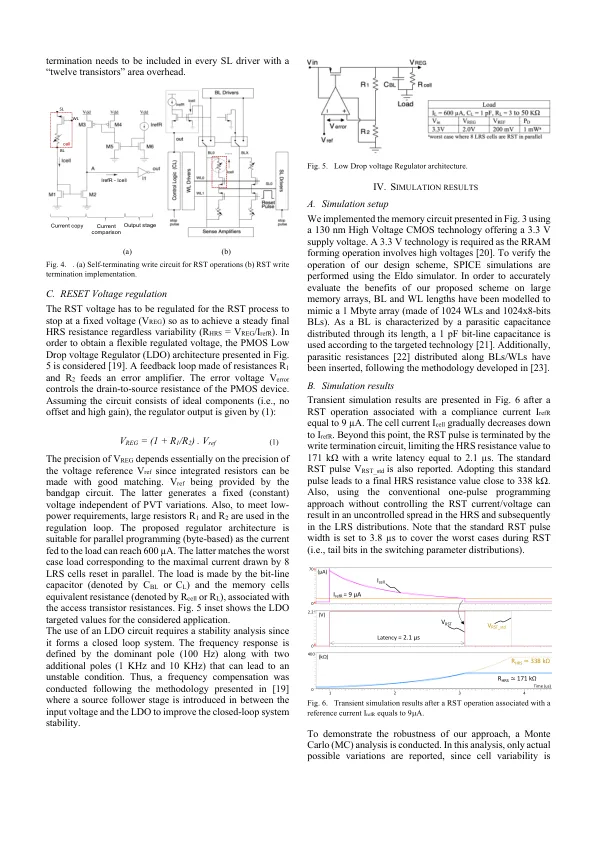

摘要 — 电阻式 RAM (RAM) 固有的可变性被广泛认为是广泛采用该技术的主要障碍。此外,我们越深入高阻状态 (HRS),可变性就越高。在此背景下,本文提出了电路级设计策略来减轻 HRS 的可变性。在 RESET 操作期间,编程电流受到严格控制,同时调节 RRAM 单元两端的电压。从设计的角度来看,写入终止电路用于不断感测编程电流并在达到首选 RESET 电流时停止 RESET 脉冲。写入终止与电压调节器相结合,可严格控制 RESET 电压。本文首先回顾了 RRAM 可变性现象。然后,开发了一种优化的编程方案来控制 HRS 状态以接近零可变性。与经典的固定脉冲编程方案相比,可变性降低了 99%。

HRS 状态下零变异性电阻式 RAM 的设计考虑