机构名称:

¥ 2.0

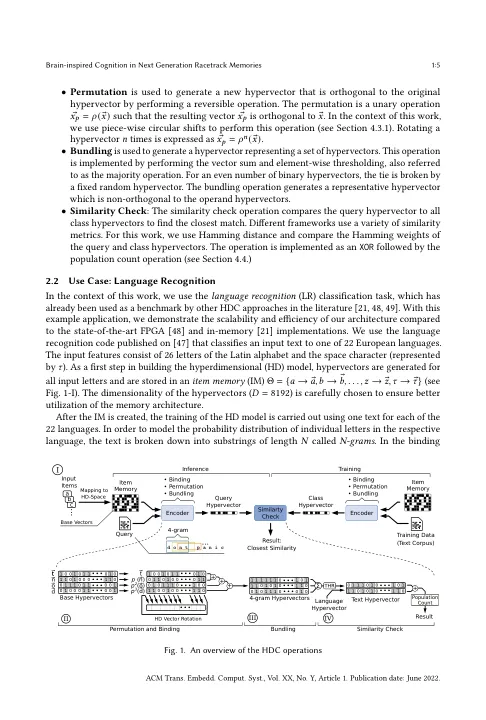

超维计算 (HDC) 是一种新兴的计算框架,其灵感来自大脑,它对具有数千个维度的向量进行操作以模拟认知。与对数字进行操作的传统计算框架不同,HDC 与大脑一样,使用高维随机向量,并且能够进行一次性学习。HDC 基于一组定义明确的算术运算,具有很强的错误恢复能力。HDC 的核心操作以批量逐位方式操纵 HD 向量,提供了许多利用并行性的机会。不幸的是,在传统的冯·诺依曼架构中,HD 向量在处理器和内存之间的连续移动会使认知任务变得非常缓慢且耗能。硬件加速器只能略微改善相关指标。相比之下,即使是内存中 HDC 框架的部分实现也可以提供相当大的性能/能量增益,正如之前使用忆阻器的工作所证明的那样。本文介绍了一种基于赛道内存 (RTM) 的架构,用于在内存中执行和加速整个 HDC 框架。所提出的解决方案利用 RTM 中跨多个域的读取操作(称为横向读取 (TR))来实现异或 (XOR) 和加法运算,从而只需极少的额外 CMOS 电路。为了最大限度地减少 CMOS 电路开销,提出了一种基于 RTM 纳米线的计数机制。以语言识别为示例工作负载,所提出的 RTM HDC 系统与最先进的内存实现相比,将能耗降低了 8.6 倍。与使用 FPGA 实现的专用硬件设计相比,基于 RTM 的 HDC 处理在整体运行时间和能耗方面分别实现了 7.8 倍和 5.3 倍的提升。

下一代赛道记忆中的大脑启发认知

主要关键词