机构名称:

¥ 1.0

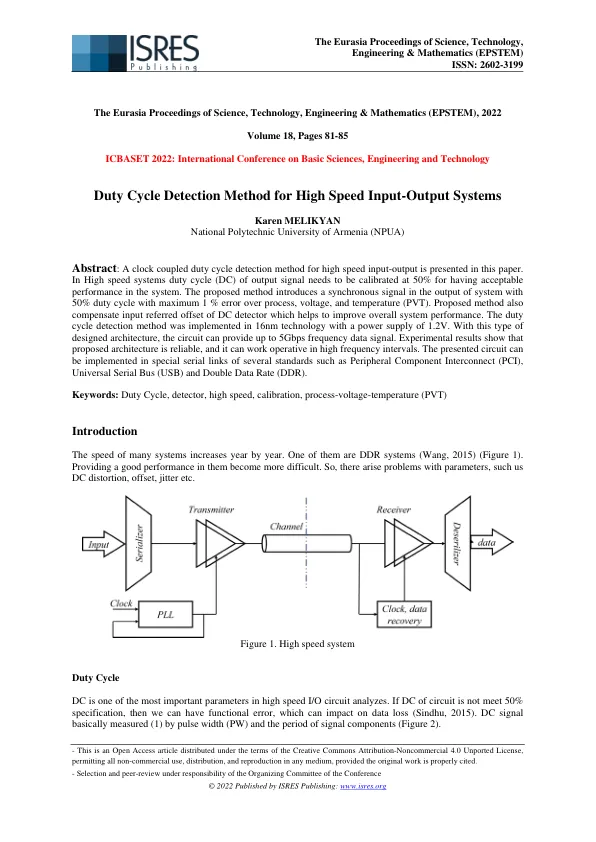

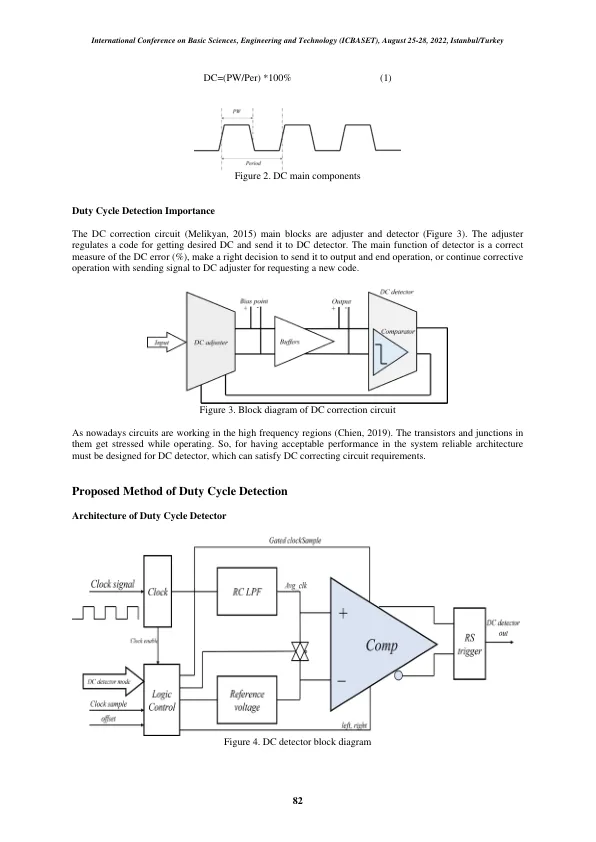

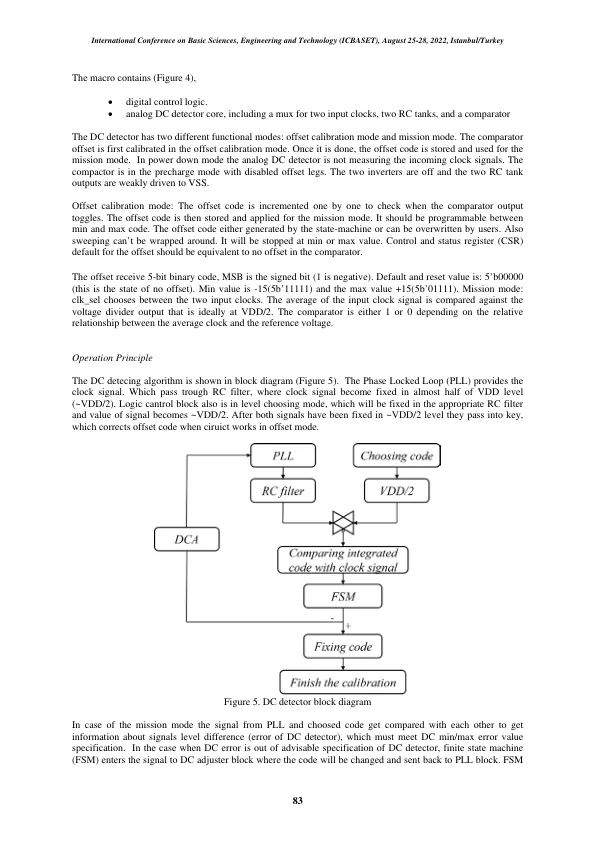

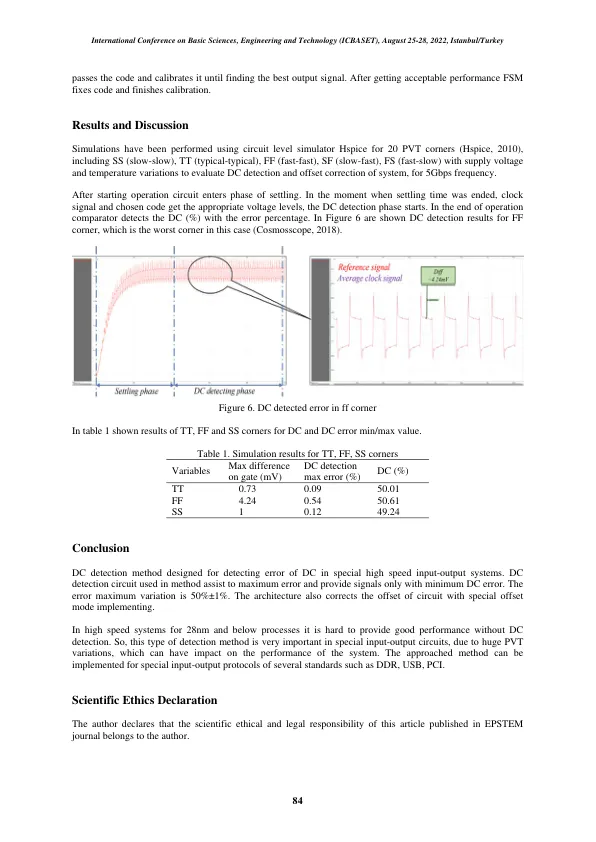

Karen MELIKYAN 亚美尼亚国立理工大学 (NPUA) 摘要:本文介绍了一种用于高速输入输出的时钟耦合占空比检测方法。在高速系统中,输出信号的占空比 (DC) 需要校准为 50% 才能在系统中获得可接受的性能。所提出的方法在系统输出中引入一个同步信号,占空比为 50%,最大工艺、电压和温度 (PVT) 误差为 1%。所提出的方法还补偿了 DC 检测器的输入参考偏移,这有助于提高整体系统性能。占空比检测方法采用 16nm 技术实现,电源为 1.2V。采用这种设计的架构,电路可以提供高达 5Gbps 频率的数据信号。实验结果表明,所提出的架构可靠,并且可以在高频间隔内工作。所提出的电路可以在多种标准的特殊串行链路中实现,例如外围组件互连 (PCI)、通用串行总线 (USB) 和双倍数据速率 (DDR)。关键词:占空比、检测器、高速、校准、工艺电压温度 (PVT) 简介 许多系统的速度逐年提高。DDR 系统就是其中之一 (Wang, 2015)(图 1)。在这些系统中提供良好的性能变得更加困难。因此,出现了参数问题,例如直流失真、偏移、抖动等。

高速输入输出系统的占空比检测方法

主要关键词