机构名称:

¥ 1.0

摘要 —快速二进制压缩器是许多基本数字计算单元的主要组成部分。本文提出了一种具有快速进位生成逻辑的高速 (7,2) 压缩器。进位生成逻辑基于排序网络,它可以在 2 个逻辑级内生成进位位,而不是像以前的教科书全加器那样需要 3 个级。与调整后的全加器逻辑配合,提出的 (7,2) 压缩器仅使用 11 个基本逻辑级即可实现。在具有 7 行 8 列的二进制数组中测试了这种新设计,结果表明该设计比以前的设计具有更高的性能。该方法适用于乘法设计或其他密码硬件模块中的高性能情况。索引术语 —(7,2) 压缩器、乘法器、全加器、排序网络

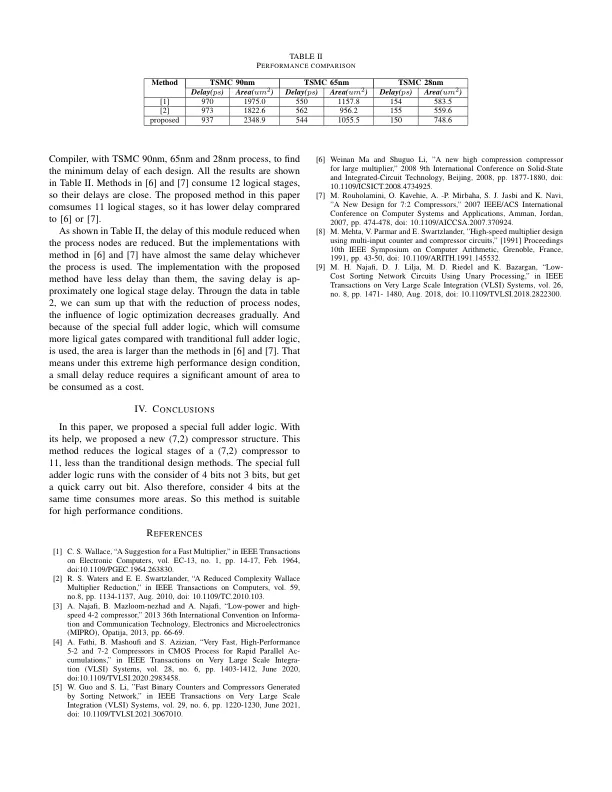

采用快速承载式高速(7,2)压缩机...