机构名称:

¥ 1.0

近年来,逻辑器件的量产技术已经发展到 3nm 技术节点[1]。未来,英特尔、三星、台积电将继续利用 2nm 技术节点的新技术,如环栅场效应晶体管 (GAAFET) [2,3]、埋入式电源线 (BPR) [4–8],来优化逻辑器件的功耗、性能、面积和成本 (PPAC)。然而,横向器件的微缩越来越困难,流片成本已令各大设计公司难以承受。同时,垂直器件将成为未来 DRAM 器件中 4F2 单元晶体管的有竞争力的候选者 [9–13]。关于垂直器件的研究报道很多,大致可分为两条路线。“自下而上”路线利用金属纳米粒子诱导催化,实现垂直纳米线沟道的生长 [14,15]。然而该路线存在金属元素问题,如金污染,与标准CMOS工艺不兼容。另外,通过光刻和刻蚀工艺“自上而下”制作垂直晶体管器件的方法已被三星和IBM报道[16,17]。然而该路线也存在一些问题,例如器件栅极长度和沟道厚度难以精确控制,并且该路线中栅极无法与垂直器件的源/漏对齐。为了解决上述问题,提出了基于SiGe沟道的垂直夹层环绕栅极(GAA)场效应晶体管(VSAFET),其在栅极和源/漏之间具有自对准结构[18–21]。最近,垂直C形沟道纳米片

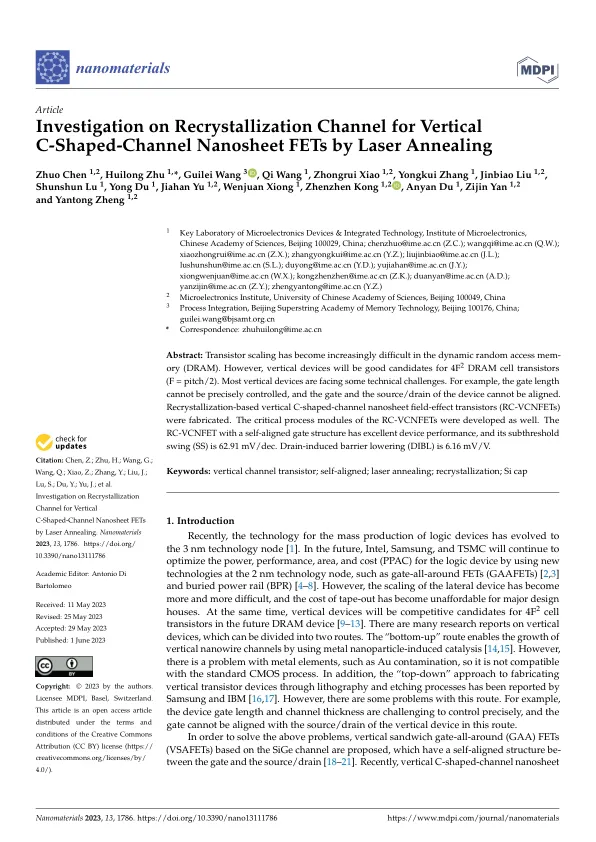

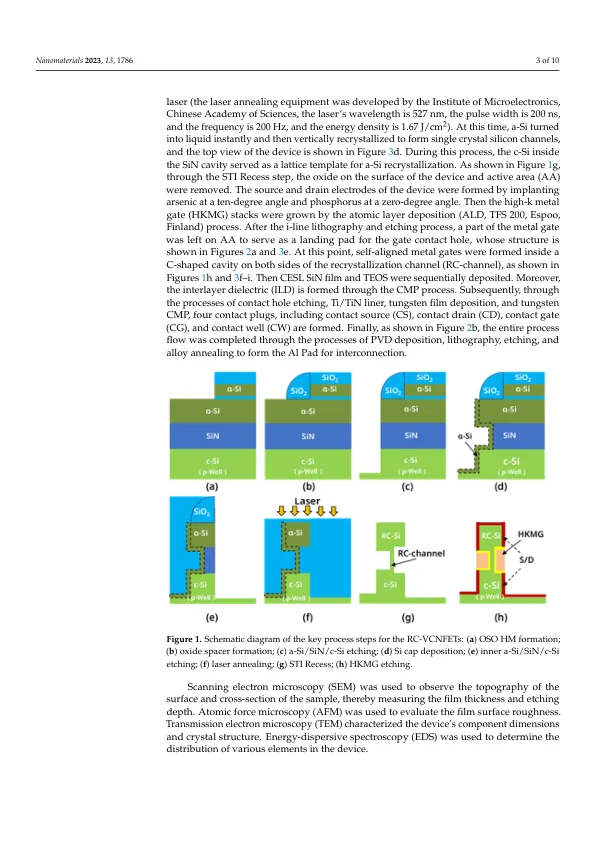

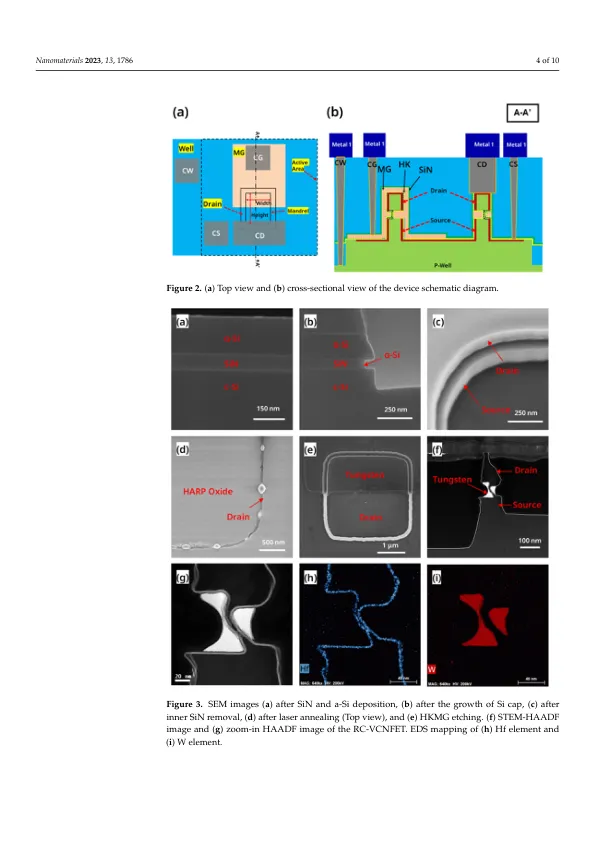

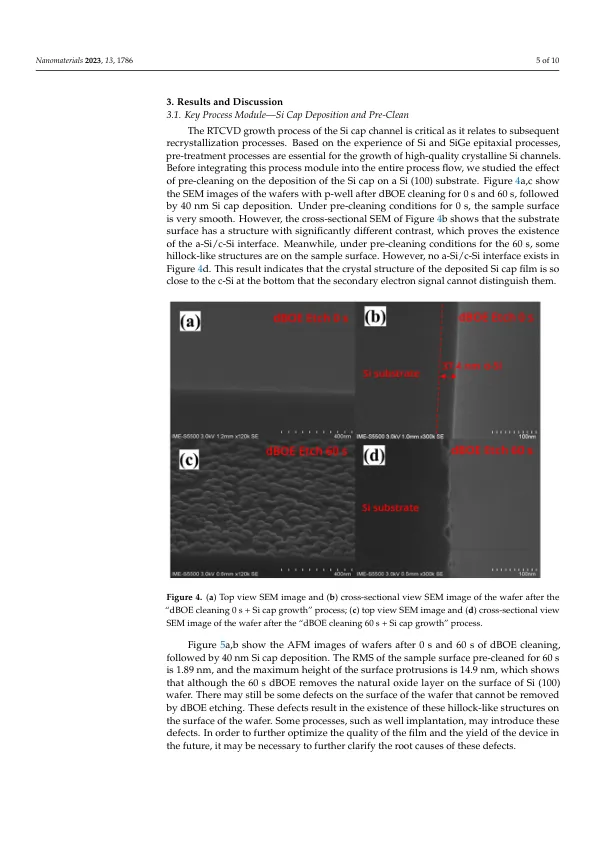

立式碳钢再结晶通道的研究...