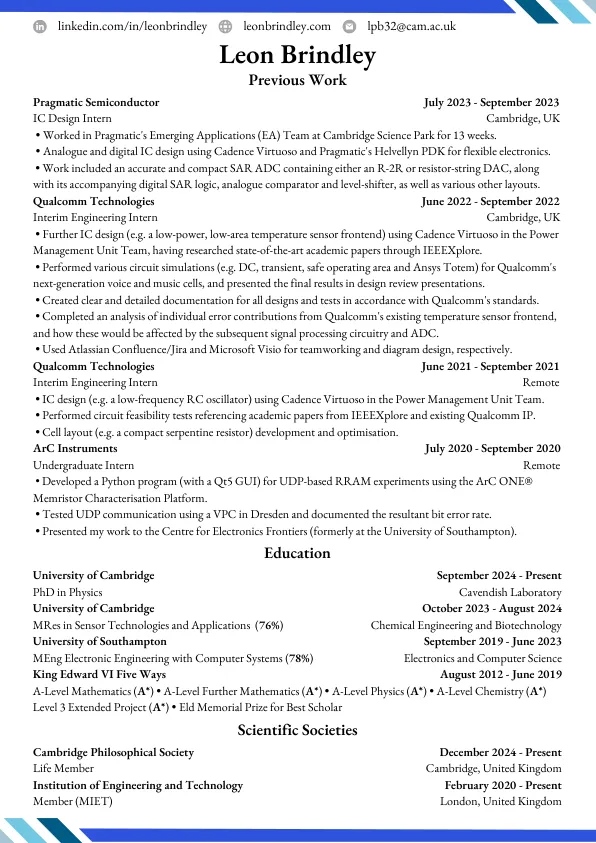

务实的半导体2023年7月 - 2023年9月IC设计实习生,英国剑桥•在务实的新兴应用程序(EA)在剑桥科学公园工作了13周。•使用Cadence Virtuoso和Pragmatic的Helvellyn PDK用于灵活电子产品的模拟和数字设计。•工作包括一个精确而紧凑的SAR ADC,其中包含R-2R或电阻弦DAC,以及其随附的数字SAR逻辑,模拟比较器和级别转换器以及其他各种布局。Qualcomm Technologies 2022年6月 - 2022年9月临时工程实习生,英国•进一步的IC设计(例如,通过IEEEXPLORE研究了最先进的学术论文,使用Cadence Virtuoso使用Cadence Virtuoso,使用Cadence Virtuoso。•进行了各种电路模拟(例如DC,瞬态,安全操作区域和ANSYS图腾),用于高通公司的下一代语音和音乐单元,并在设计审查演示文稿中介绍了最终结果。•根据高通公司的标准为所有设计和测试创建了清晰详细的文档。•完成了对高通公司现有温度传感器前端的个人错误贡献的分析,以及这些分析将如何受到随后的信号处理电路和ADC的影响。•分别用于团队合作和图表设计的Atlassian Confluence/Jira和Microsoft Visio。高通技术2021年6月 - 2021年9月临时工程实习生•IC设计(例如使用电力管理单位团队中的Cadence Virtuoso的低频RC振荡器)。•单元格布局(例如•执行的电路可行性测试参考了IEEXPLORE和现有高通IP的学术论文。紧凑的蛇形电阻器)的开发和优化。ARC Instruments 2020年7月 - 2020年9月本科实习生•使用ARCOne®Memristor表征平台开发了基于UDP的RRAM实验的Python程序(带有QT5 GUI)。•使用Dresden中的VPC测试了UDP通信,并记录了结果位错误率。•将我的工作介绍给电子领域中心(以前在南安普敦大学)。

课程(2025年1月)

主要关键词