机构名称:

¥ 1.0

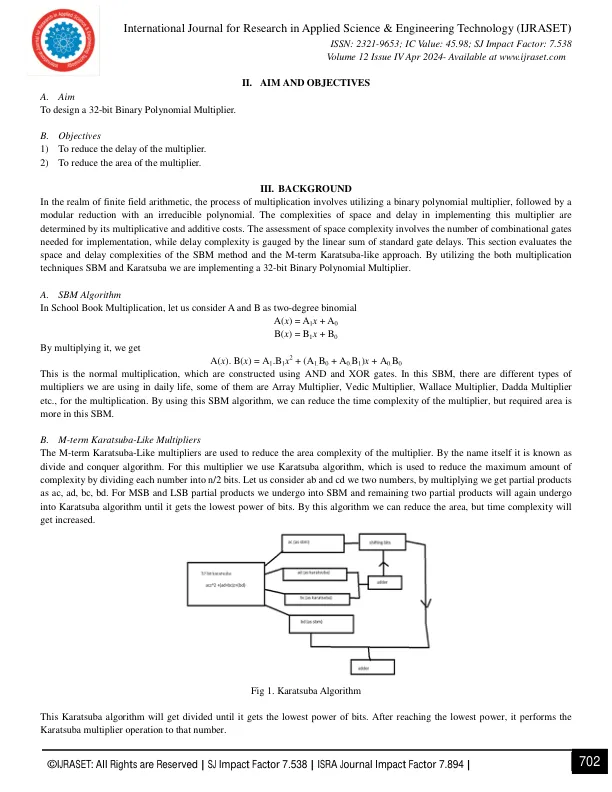

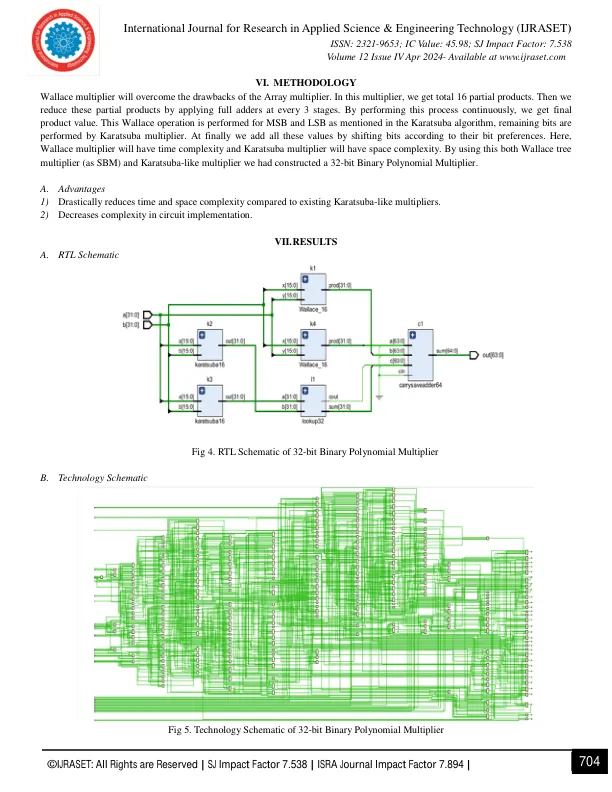

工程学院,奎师那dt。,安得拉邦摘要:有限的场乘法在加密电路中起着至关重要的作用,因为其广泛应用。但是,由于其复杂性,这些乘法的建筑电路构成了重大挑战。为了减轻这种情况,使用Karatsuba算法,将每个数字分为N/2位以降低空间复杂性。这种方法降低了空间的复杂性,但也会增加时间复杂性。在我们的研究中,我们引入了一种混合方法,实施了类似Karatsuba的乘数,该乘数结合了Karatsuba和SBM(学校图书乘法)技术的元素。在拟议的设计中,我们用华莱士树乘法器替换阵列乘数,以进一步提高设计性能。这种组合有效地降低了时间和空间的复杂性。根据报告的设备利用和潜伏期,我们的发现表明,所提出的乘数在速度和效率方面比标准的Karatsuba乘数优于标准的Karatsuba乘法器,尤其是在该地区 - 德莱产品指标。关键字:二进制多项式乘数,现场可编程的门阵列(FPGA),有限的场乘法,华莱士树乘数,M-Term Karatsuba类似。

13 I 2025年1月https://doi.org/10.22214/ ...

主要关键词