机构名称:

¥ 1.0

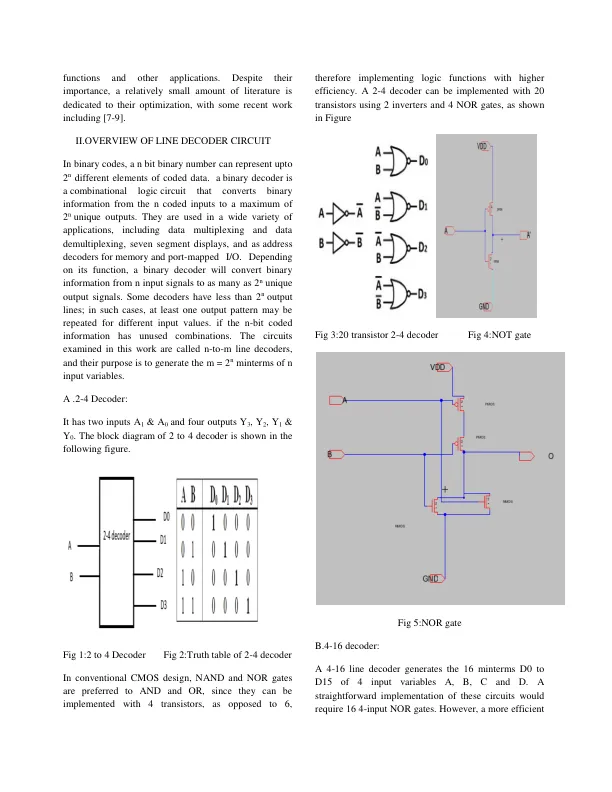

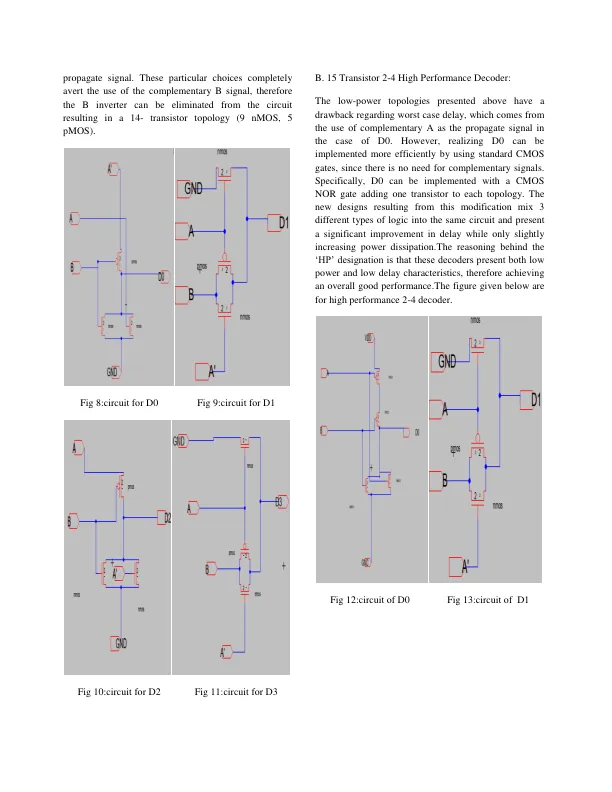

摘要-本文介绍了一种线路解码器的混合逻辑设计方法,结合了传输门逻辑和传输晶体管。针对 2-4 解码器,提出了两种新型拓扑结构:一种是旨在最小化晶体管数量和功耗的 14 晶体管拓扑结构,另一种是旨在实现高功率延迟性能的 15 晶体管拓扑结构。完整的设计是在解码器的正常模式下完成的,因此存在两种 2-4 解码器设计。此外,还设计了两个新的 4-16 解码器,使用混合逻辑 2-4 预解码器与标准 CMOS 后解码器相结合。与传统的 CMOS 解码器相比,所有提出的解码器都具有全摆幅能力和更少的晶体管数量。最后,使用 LTspice 编码在电子 VLSI 软件中对 300nm 进行了各种比较 Spice 模拟,结果表明,与 CMOS 相比,提出的电路在几乎所有情况下都具有显着的功率和延迟改进。

高性能、低功耗2-4和4-16混合设计