机构名称:

¥ 1.0

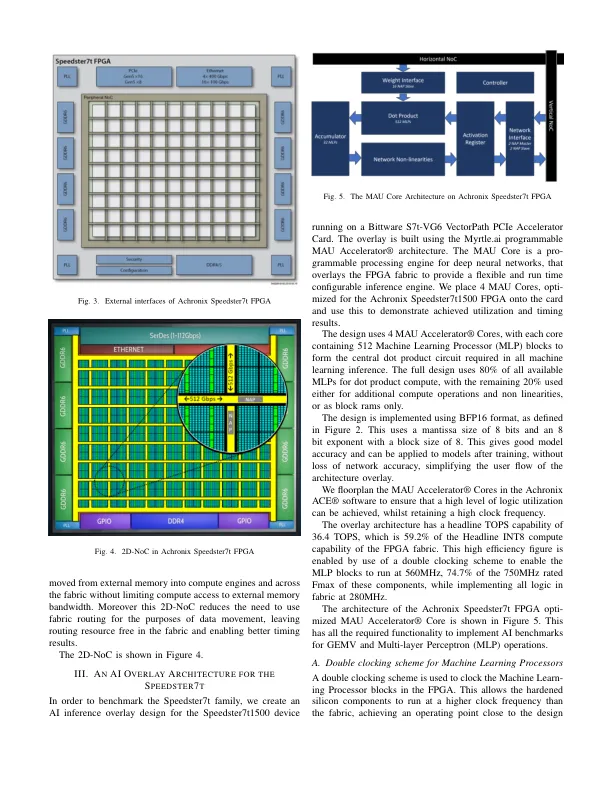

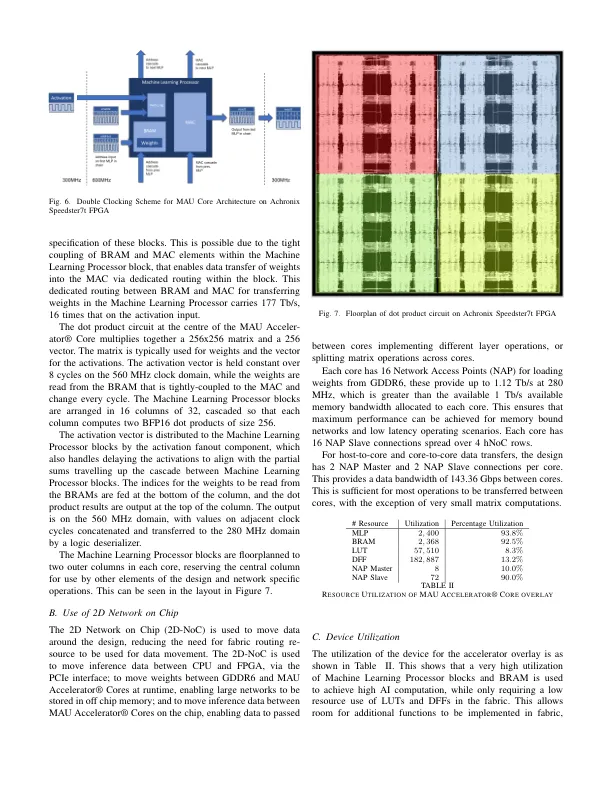

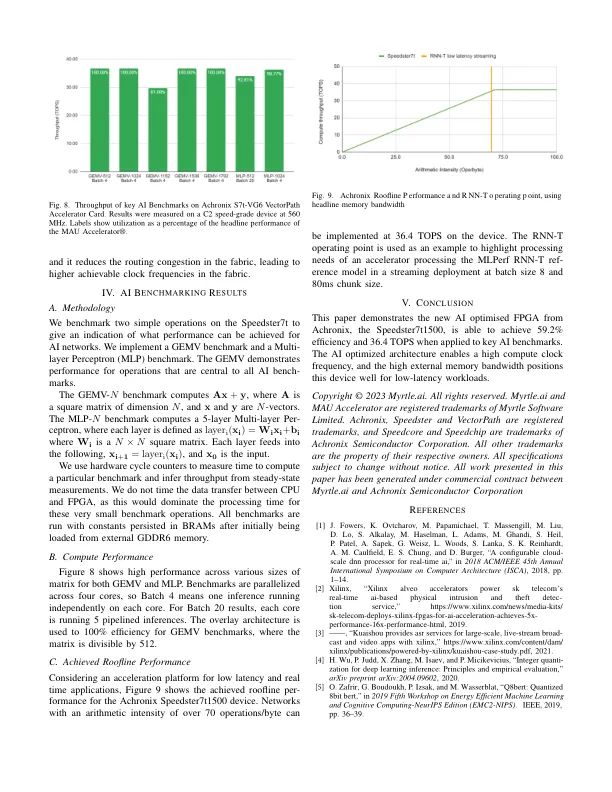

摘要 — 具有自回归关键路径或递归的机器学习网络的部署通常不能很好地利用 AI 加速器硬件。此类网络(如自动语音识别中使用的网络)必须以低延迟和确定性尾部延迟运行,以适应大规模实时应用。在本文中,我们介绍了一种推理引擎的覆盖架构,然后在 Speedster7t FPGA 上实现该架构。Speedster7t 是 Achronix Semi-conductor Corporation 生产的 AI 优化设备。我们展示了所考虑的网络类型的潜在高利用率。具体来说,我们描述了一种双时钟方法,该方法可实现 Speedster 设备中机器学习处理器块额定频率的 74.7% 的时钟频率。我们表明,该设备可以在一组标准的 AI 基准测试中实现 36.4 TOPS,并表明它可以在一系列场景中实现约 60% 的设备总体效率。然后,我们重点介绍了这种架构对于自动语音识别等低延迟实时应用的好处。

在 Achronix Speedster®7t FPGA 上进行 AI 基准测试

主要关键词