机构名称:

¥ 2.0

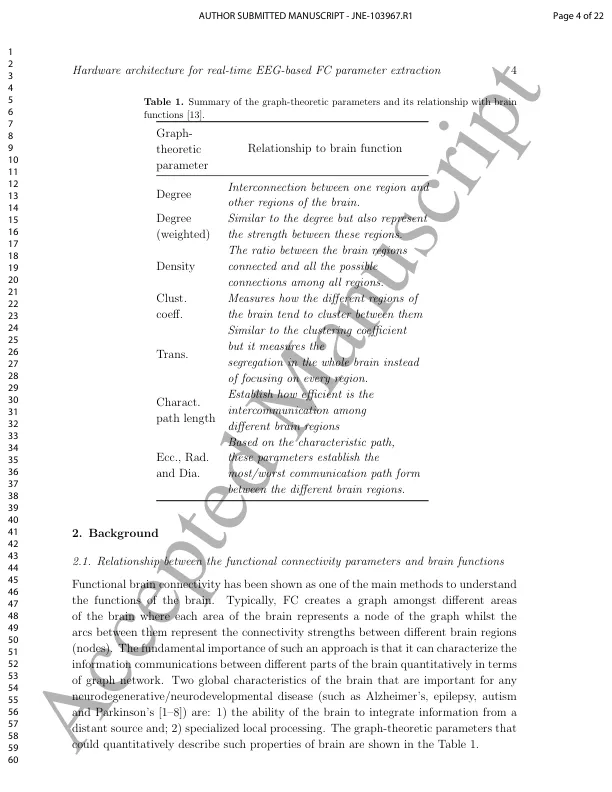

摘要。目标。设计一种新型架构,用于实时定量表征,该功能性脑连接网络来自可穿戴脑电图(EEG)。方法。我们对架构映射进行了算法,以计算相位滞后索引(PLI),以形成功能连接网络和提取一组图理论参数以定量表征这些网络。使用算法的数学定义中的近似值来优化该映射,该定义降低了其计算复杂性并产生更硬件的实现。主要结果。该体系结构是为19通道EEG系统开发的。系统可以在131 µs的总时间内计算所有功能连接参数,利用71%的逻辑资源,并在Stratix IV IV EP4SGX22330K FPGA中实现时在22.16 MHz操作频率下显示51.84 MW动态功耗。我们的分析还表明,该系统占据了相当于约937K 2输入NAND大门的面积,估计使用90 nm CMOS应用程序的估计功耗为39.3 MW,在0.9 V电源下为39.3 MW。明显的能力。所提出的体系结构可以计算功能性大脑连接性,并在低功耗中实时提取图理论参数。此特征使架构非常适合诸如可穿戴闭环神经反馈系统之类的应用,在该系统中,必须不断监视大脑活动和EEG快速处理以控制适当的反馈。

基于实时EEG的功能大脑连接参数提取

主要关键词