机构名称:

¥ 1.0

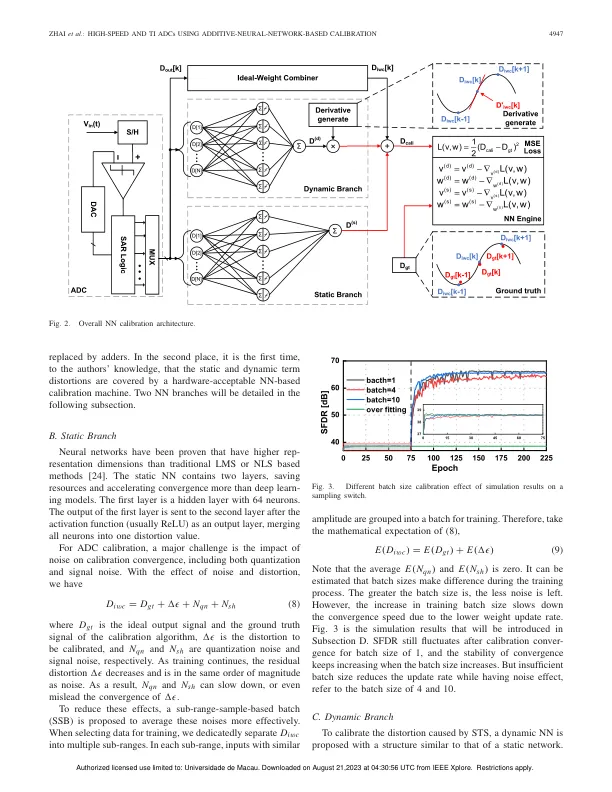

摘要 - 本文提出了一种基于神经网络的数字校准算法,用于高速和时间间隔(TI)ADC。与先前的方法相反,所提出的工作依赖于相关的非线性失真校正,而无需事先了解ADC架构特征。动态校准首先用于补偿相关的失真。提出了两个培训优化,包括基于子范围的批处理方案和递归前景共校准流量,以减少错误和过度插入并进一步节省硬件资源。还研究了具有分布重量和共享权重方法的交织ADC的实用校准引擎。为了证明该方法的有效性,通过两个制造的ADC原型验证了校准引擎,一个5 GS/S 16向交织ADC和625 ms/s Interave-SAR辅助辅助管道ADC。测量结果表明,在校准之前和之后,针对不同频率输入,SFDR在16.9dB和36.4dB之间提高。为了在准确性和功耗之间取舍,在FPGA和28NM CMOS技术上都实施了量化和修剪的发动机。实验结果表明,硅的专用校准以333MHz时钟速率消耗8.64MW,0.9V电源。测量结果表明,量化的硬件实现仅在SFDR中损失0.4-4 dB。

使用添加剂...

主要关键词