机构名称:

¥ 1.0

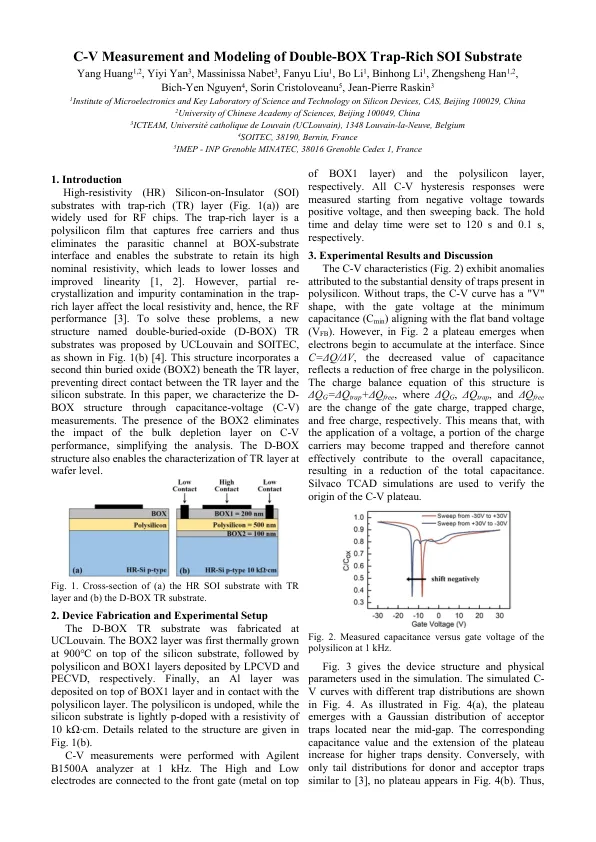

高抗性(HR)硅在胰上石(SOI)底物,具有富含陷阱的(TR)层(图。1(a))广泛用于RF芯片。富含陷阱的层是一种捕获自由载体并因此消除盒子基底界面处的寄生通道的多层膜,使底物能够保留其高标称电阻率,从而导致较低的损失并改善线性性[1,2]。然而,捕集层中的部分结晶和杂质污染会影响局部电阻率,因此,RF性能[3]。为了解决这些问题,Uclouvain和Soitec提出了一种名为Double-Buried-Oxide(D-Box)TR底物的新结构,如图1(b)[4]。该结构在TR层下方结合了第二个薄氧化物(Box2),以防止TR层和硅基板之间的直接接触。在本文中,我们通过电容 - 电压(C-V)测量来表征D框结构。Box2的存在消除了整体耗竭层对C-V性能的影响,从而简化了分析。D-box结构还可以在晶圆级别表征TR层。

C-V测量和双盒陷阱富含SOI底物的建模