机构名称:

¥ 1.0

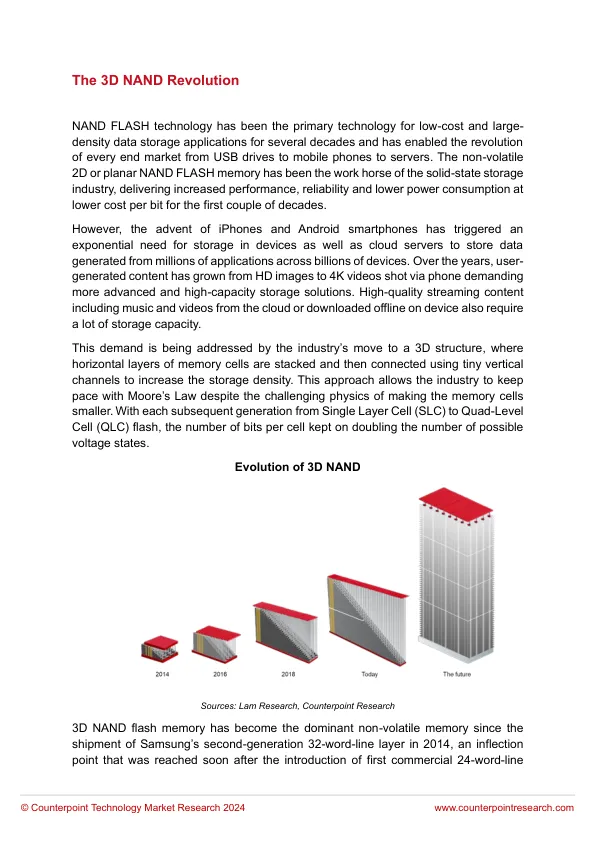

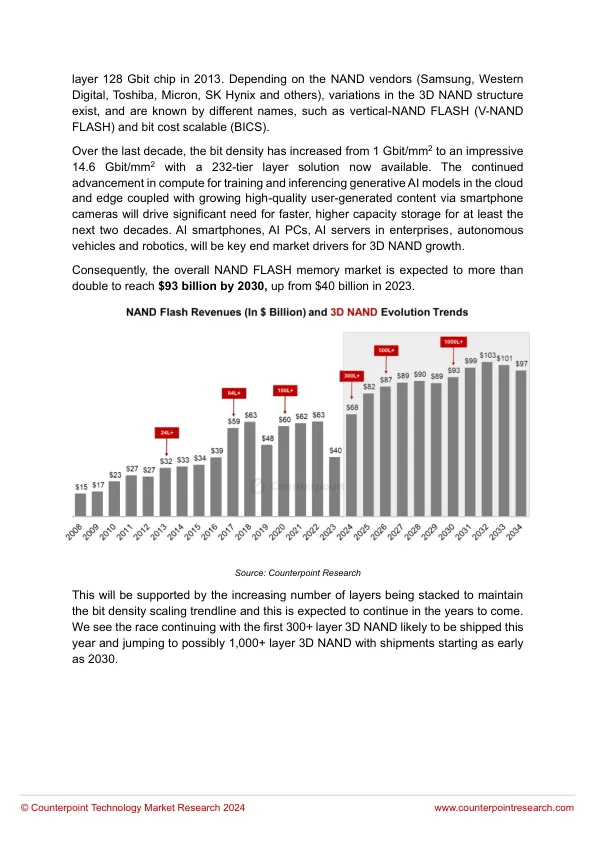

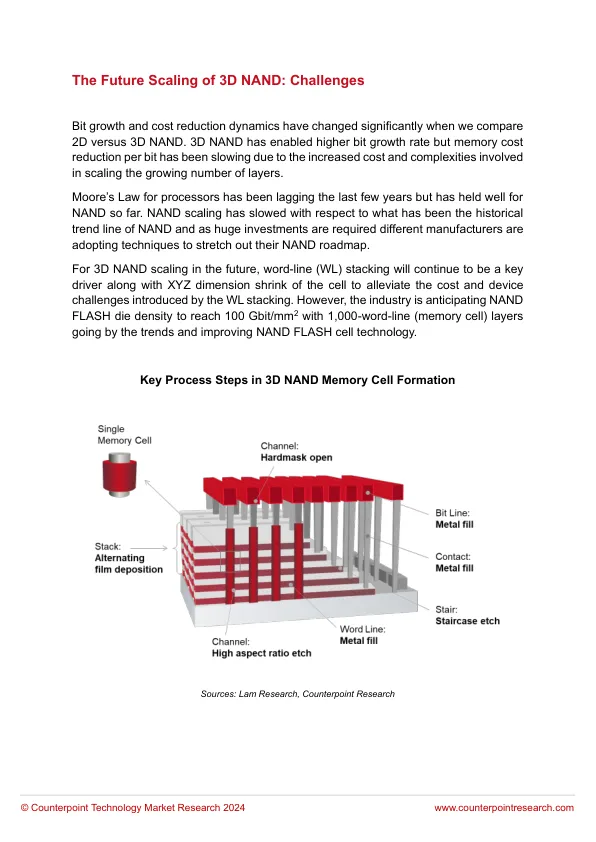

3D NAND垂直堆栈缩放缩放量主要是在膜沉积和蚀刻方面引起的挑战,这与设备通过功能尺寸减小进行缩放不同。与图案,隔离并连接垂直集成的3D存储器设备,需要难以高纵横比(HAR)蚀刻。通常将孔或沟槽的纵横比定义为深度与孔或沟槽宽度的比率。3D NAND制造中的关键过程包括替代堆栈膜沉积,高纵横比蚀刻和文字线金属化。找到位密度,读写速度,功率,可靠性和成本之间的平衡对于应用至关重要。当我们在结构中添加更多层,并且还有额外的资本支出,随着层的数量增加,增加更多的存储容量变得越来越昂贵。

在人工智能时代将缩放到1,000层3D NAND -MEDISEROMER