机构名称:

¥ 1.0

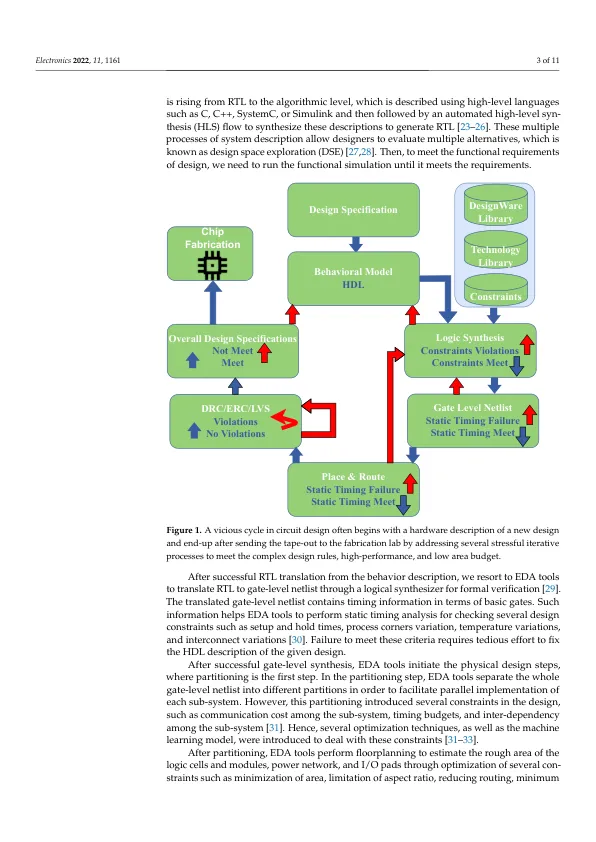

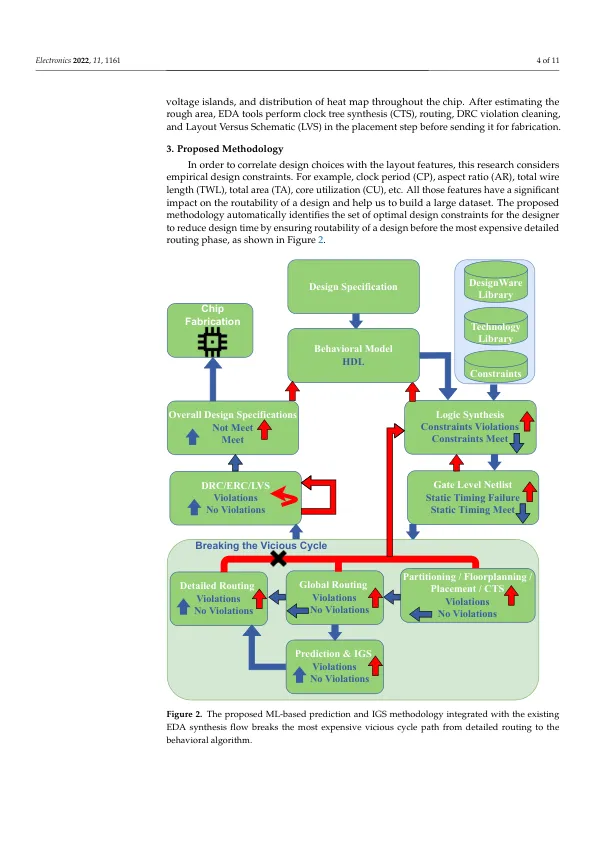

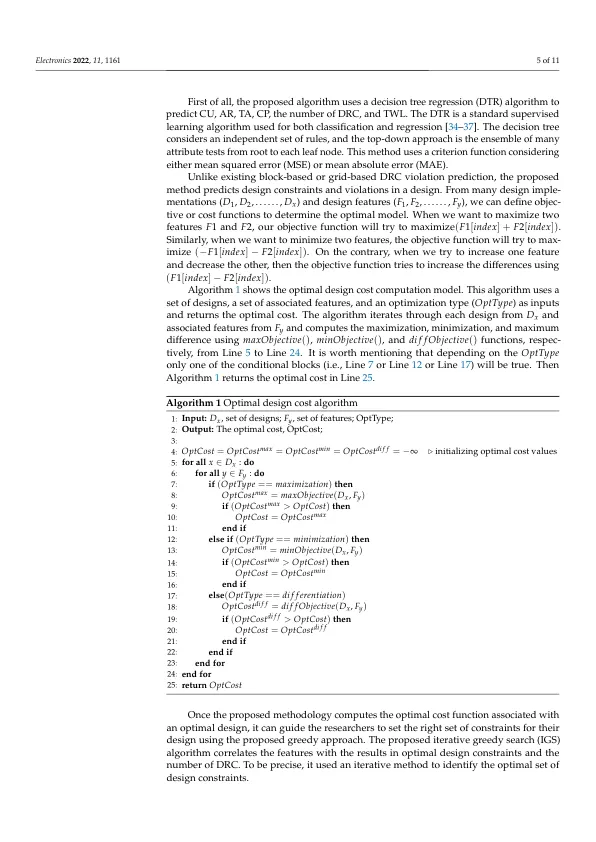

摘要:DARPA POSH 计划与研究界产生共鸣,并指出工程生产力已落后于摩尔定律,导致领先技术节点的 IC 设计成本过高。主要原因是完成设计实施需要大量计算资源、昂贵工具,甚至需要很多天的时间。然而,在此过程结束时,一些设计无法满足设计约束并变得无法布线,从而形成恶性电路设计循环。因此,设计人员必须在设计修改后重新运行整个过程。本研究采用机器学习方法自动识别设计约束和设计规则检查 (DRC) 违规问题,并通过迭代贪婪搜索帮助设计人员在漫长的详细布线过程之前识别具有最佳 DRC 的设计约束。所提出的算法实现了高达 99.99% 的设计约束预测准确率,并减少了 98.4% 的 DRC 违规,而面积损失仅为 6.9%。

快速 IC 设计空间探索的可行性预测