机构名称:

¥ 1.0

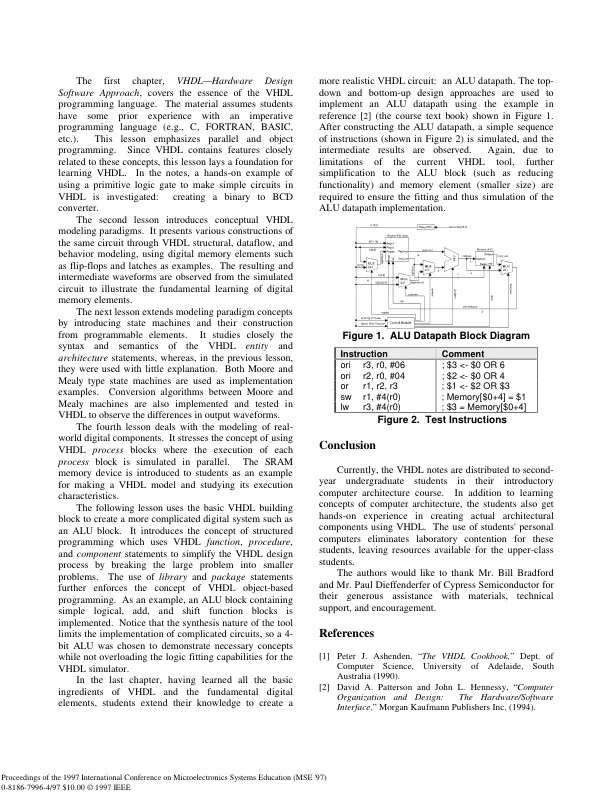

VHDL 是一种超高速集成电路 (VHSIC) 硬件描述语言,已成为设计和测试使用数千个门的复杂数字系统的重要工具。由于其简单但强大的建模能力,VHDL 在数字工程领域越来越受欢迎。此外,VHDL 语言已经通过 IEEE 标准化过程发展起来。虽然 VHDL 作为一种数字建模和硬件综合工具在业界已经成熟,但在学术界,作为数字系统设计教学工具,尤其是本科课程,VHDL 面临着许多障碍。第一个问题是学生在课外使用 VHDL 工具以缓解学校实验室资源争夺的问题。由于成本低廉和广泛吸引力,个人电脑已成为学生家庭使用的非常常见的工具。然而,目前还没有适合学生预算的 VHDL 程序。理想的 VHDL 工具应该花费学生不超过一本教科书的价格。第二个问题是 VHDL 学习主题的重点。对于刚开始学习计算机工程本科生来说,学术界使用 VHDL 的目标与工业使用目标不同。工业环境需要为具有丰富数字经验但没有 VHDL 背景的人提供课程。因此,当前的 VHDL 参考资料和教材提供的课程面向经验丰富的数字设计师,这使得刚开始学习工程的学生(缺乏这种背景)很难掌握

计算机体系结构VHDL教学

主要关键词