机构名称:

¥ 2.0

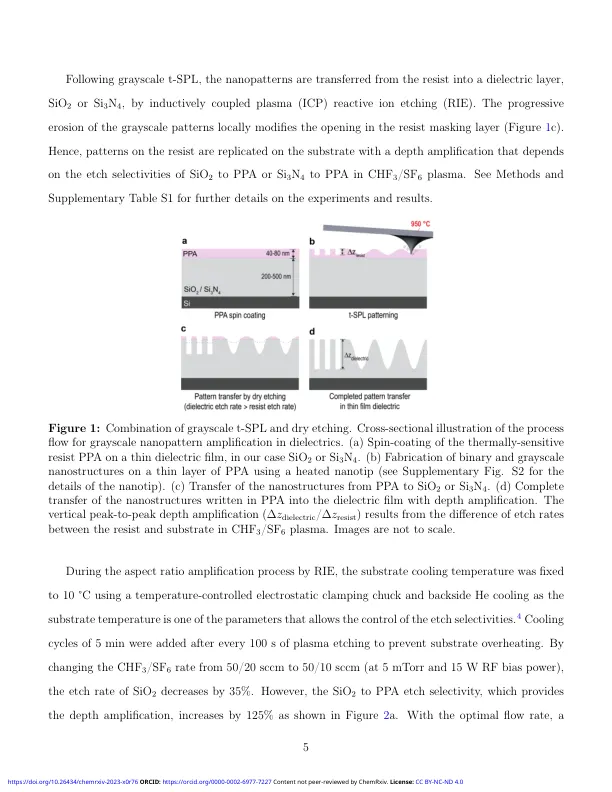

图 1:灰度 t-SPL 与干法蚀刻的组合。电介质中灰度纳米图案放大工艺流程的横截面说明。(a)在薄电介质膜(在我们的例子中为 SiO 2 或 Si 3 N 4 )上旋涂热敏抗蚀剂 PPA。(b)使用加热的纳米尖端在薄 PPA 层上制造二元和灰度纳米结构(有关纳米尖端的详细信息,请参阅补充图 S2)。(c)将纳米结构从 PPA 转移到 SiO 2 或 Si 3 N 4 。(d)通过深度放大将写入 PPA 中的纳米结构完全转移到电介质膜中。垂直峰峰深度放大(∆ z 电介质/∆ z 抗蚀剂)是由 CHF 3 /SF 6 等离子体中抗蚀剂和基板之间的蚀刻速率差异造成的。图像未按比例绘制。

结合热扫描探针光刻和干法...