机构名称:

¥ 1.0

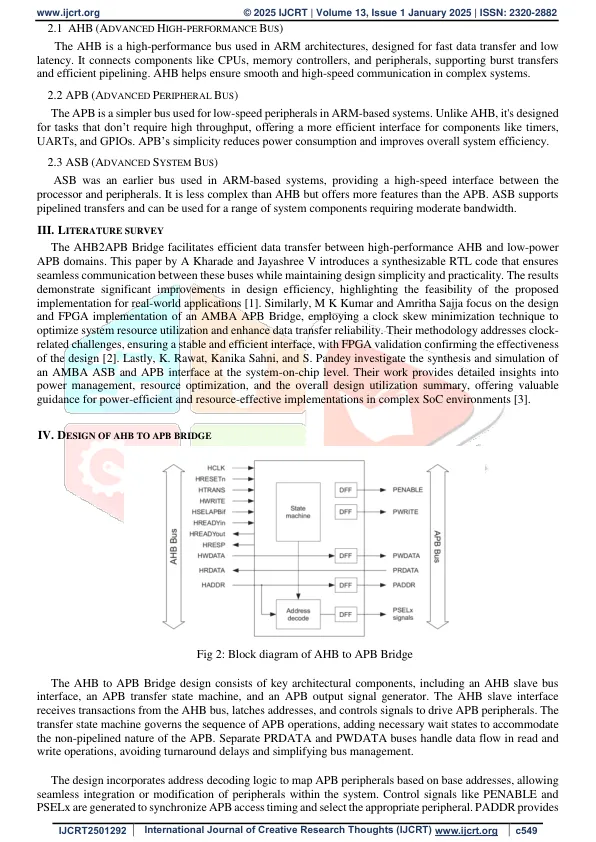

I. 引言 随着嵌入式系统变得越来越复杂,高速和低功耗组件之间的有效通信变得至关重要。ARM 的 AMBA(高级微控制器总线架构)协议提供了一个标准化框架来满足这一要求。在 AMBA 中,高级高性能总线 (AHB) 支持快速数据传输,而高级外设总线 (APB) 则专注于外设的低功耗操作。为了确保这两条总线之间的无缝交互,可靠的桥接对于高效的数据传输和系统集成是必不可少的。本研究以使用 Verilog 设计和实现 AHB 到 APB 桥接为中心。该桥接促进了高性能处理器和低功耗外设之间的互操作性,旨在优化性能并最大限度地减少延迟,同时遵守 AMBA 标准。严格的验证方法确保了其在不同用例中的可靠性,解决了总线通信中的关键挑战,并促进了嵌入式系统设计的进步。

使用 ... 设计和实现 Ahb 到 Apb 桥接器

主要关键词