机构名称:

¥ 1.0

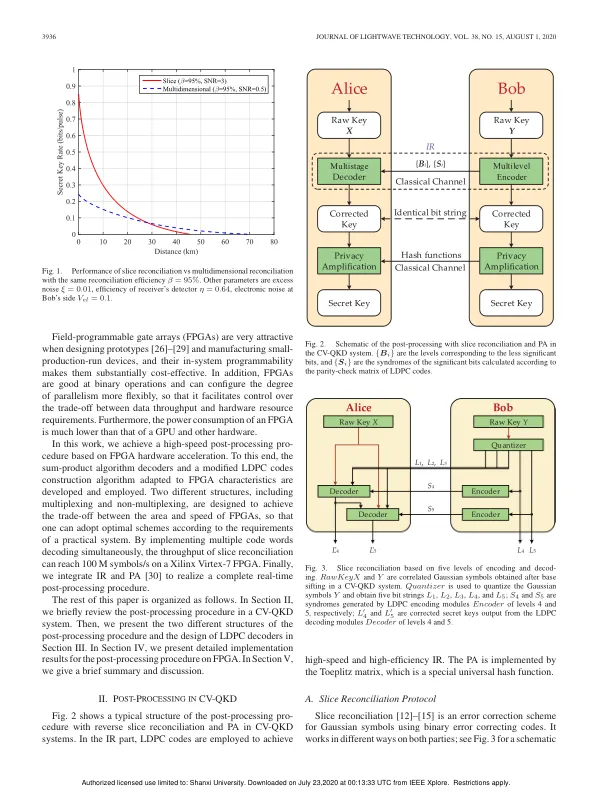

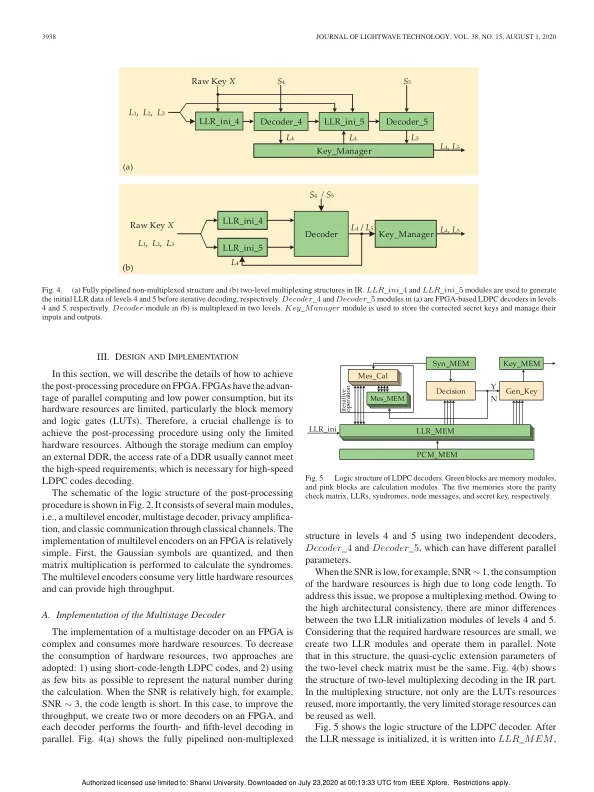

摘要 —在连续变量量子密钥分发(CV-QKD)系统中,后处理过程(包括信息协调(IR)和隐私放大(PA))的计算速度不可避免地影响实际密钥速率。IR 和 PA 可以分别使用低密度奇偶校验(LDPC)码和哈希函数并行实现。利用现场可编程门阵列(FPGA)卓越的并行处理能力,在FPGA上实现了高斯符号的高速硬件加速后处理过程。为此,开发并采用了适应FPGA特点的和积算法解码器和改进的LDPC码构造算法。设计了复用和非复用两种不同的结构来实现FPGA速度和面积之间的权衡,以便根据实际系统的要求采用最佳方案。仿真结果表明,最大吞吐量可以达到100 M 符号/秒。我们在装有 Virtex-7 XC7VX690T FPGA 的 Xilinx VC709 评估板上验证了后处理程序的正确性,并提供了在有更先进的 FPGA 可用时获得更好性能的一些可能的解决方案。该方案可轻松应用于实时密钥提取,并有效降低 CV-QKD 系统的功耗。

基于FPGA实现的连续变量量子密钥分发高速后处理

主要关键词

![机载量子密钥分发:综述 [特邀]](/simg/f/fa848b471afa8b60741d9652768fc0297159e77f.webp)