机构名称:

¥ 1.0

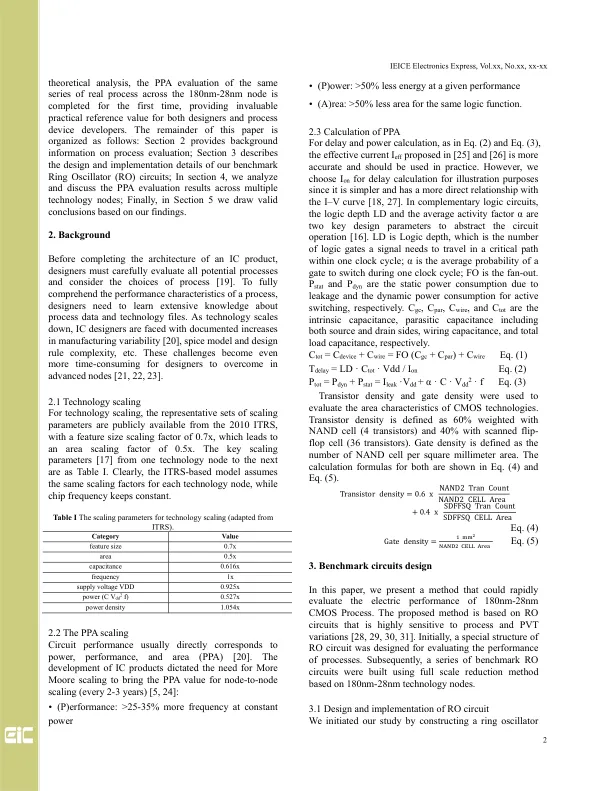

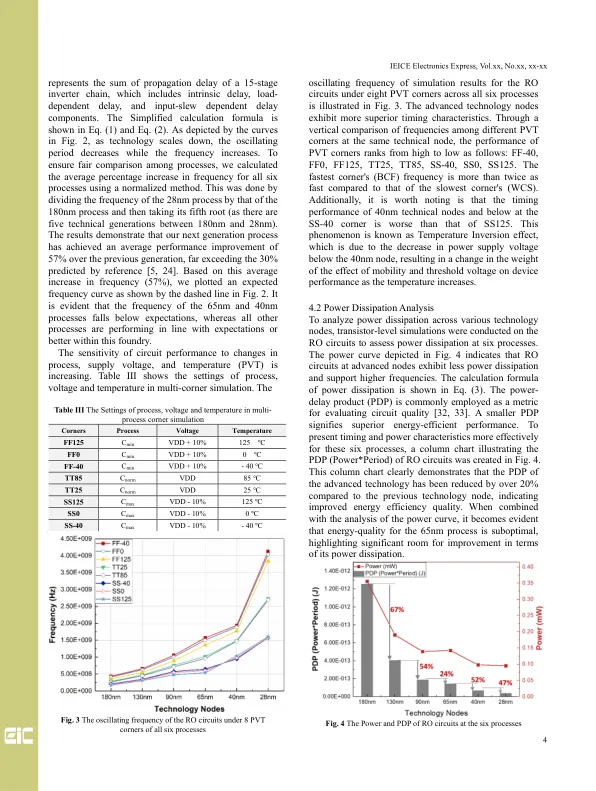

摘要 本研究提出了一种能够有效、全面评估多种技术节点的CMOS工艺的功率-性能-面积(PPA)特性的方法。根据国际半导体技术路线图(ITRS),我们采用从180nm半节距节点到28nm节点的全尺寸缩小方法,设计并实现了一系列基准环形振荡器(RO)电路。同时,我们对基于六种低泄漏(LL)工艺:180nm、130nm、90nm、65nm、40nm和28nm工艺的RO电路进行了仿真、分析和版图设计。通过纵向分析和比较这六种工艺的PPA特性,可以更好地了解工艺质量,并得出一些可靠的结论来指导设计指标。所提出的方法和基准电路可以很好地扩展到未来的先进技术节点。关键词:集成电路(IC)、PPA、RO电路、CMOS工艺、PVT 分类:集成电路(存储器、逻辑、模拟、RF、传感器)

180nm 的功率、性能和面积评估...

主要关键词