机构名称:

¥ 1.0

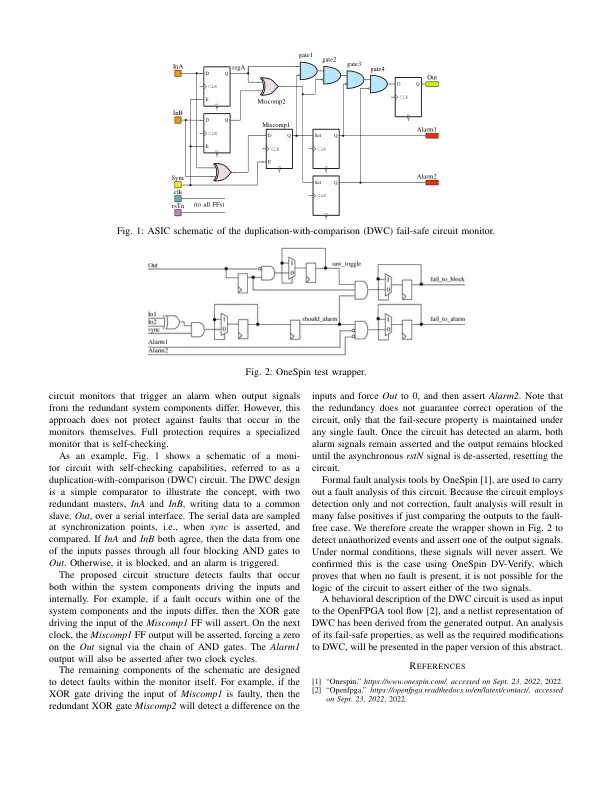

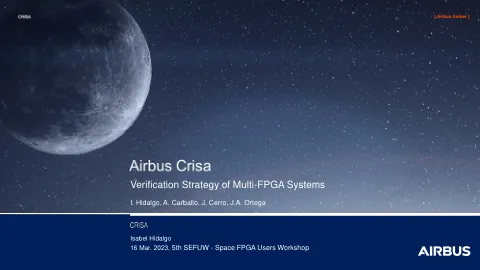

摘要 — 故障安全计算是指在发生故障时恢复到非操作安全状态的计算系统。在本文中,我们研究了电路级技术作为在现场可编程门阵列 (FPGA) 上实现故障安全计算过程的缓解策略。在使用开源工具创建的 FPGA 架构中,评估了故障效应通过 FPGA 基元(包括查找表 (LUT)、可配置逻辑块和开关盒)的传播。分析表明,与等效专用集成电路 (ASIC) 版本的故障安全电路相比,可重构架构中存在更多漏洞,因此需要更复杂的冗余电路网络和检查逻辑。提出了一种经过 ASIC 验证的故障安全监控电路版本,并将其与 FPGA 中的等效电路要求进行了比较。固定布局和布线的故障安全电路设计策略有助于减少可能的故障传播路径数量并简化故障安全故障检测电路设计。介绍并讨论了基于 FPGA 的具有报警功能的故障安全电路结构的优点和局限性,以及模拟和形式分析。

现代 FPGA 架构中的故障安全逻辑设计策略

主要关键词