机构名称:

¥ 1.0

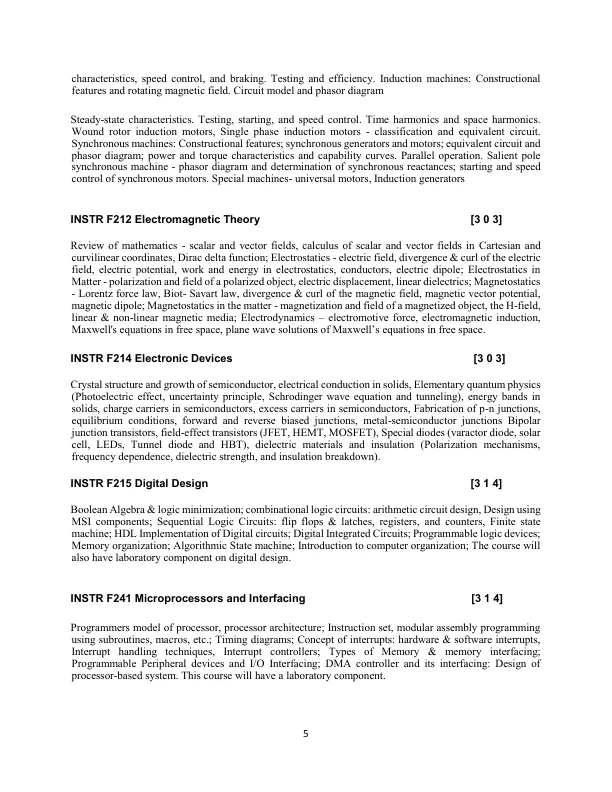

CMOS电路,寄生电容,MOS缩放技术,闩锁,匹配问题,布局中常见的质心几何形状。用于逻辑,算术和顺序块设计的数字电路设计样式;使用逻辑工作的设备尺寸;定时问题(时钟偏斜和抖动)和时钟分布技术;能源消耗的估计和最小化;功率延迟权衡,互连建模;内存体系结构,内存电路设计,感官放大器;集成电路测试的概述。基本和级联的NMOS/PMOS/CMOS增益阶段,差分放大器以及高级OPAMP设计,设备的匹配,错配分析,CMRR,PSRR和SLEW速率问题,偏移电压,高级电流镜;电流和电压参考设计,共同模式反馈电路,频率响应,稳定性和噪声问题;频率补偿技术。

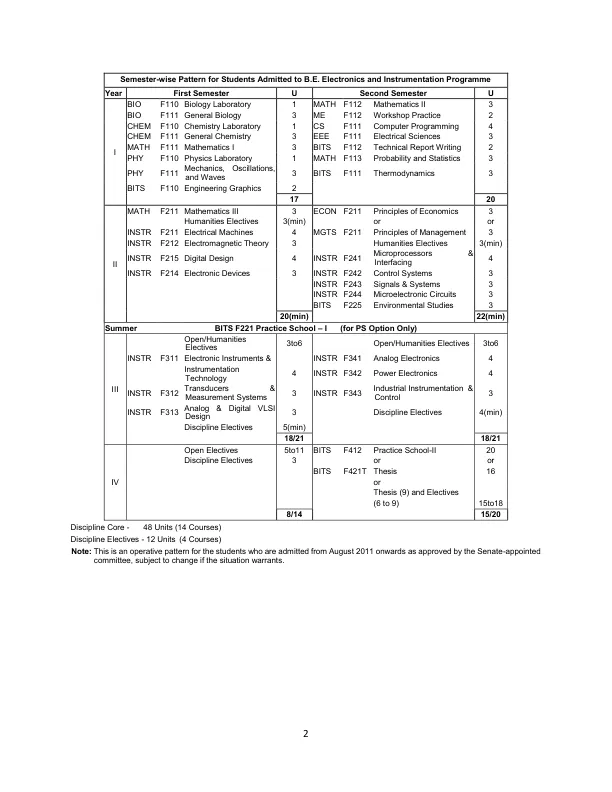

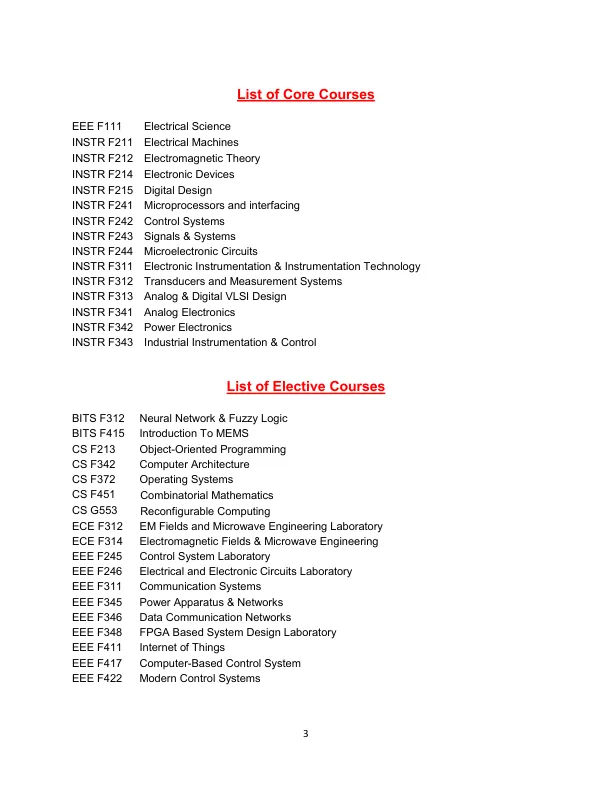

B.E.电子和仪器工程B.E.电子和仪器工程

主要关键词