机构名称:

¥ 1.0

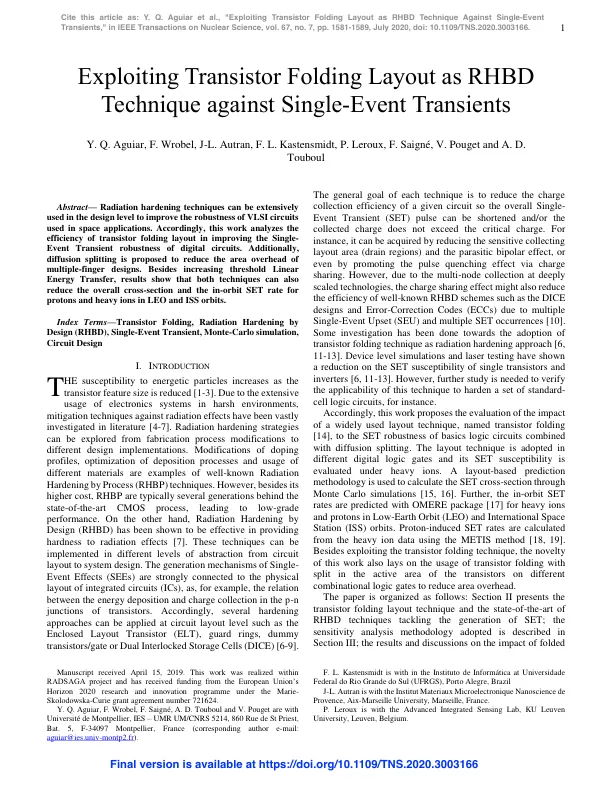

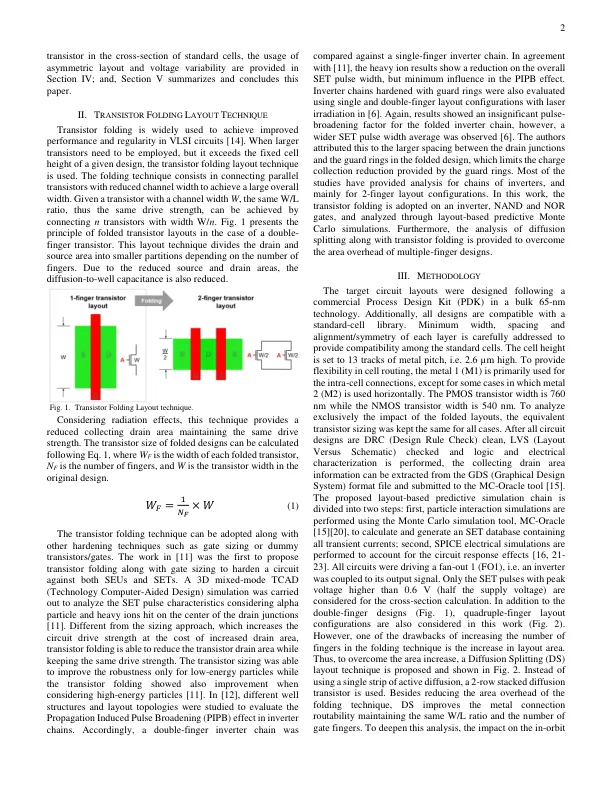

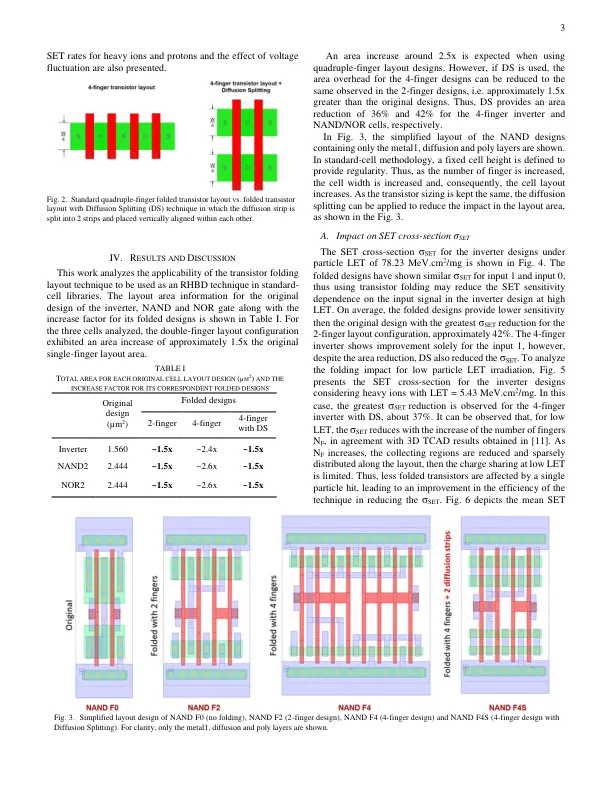

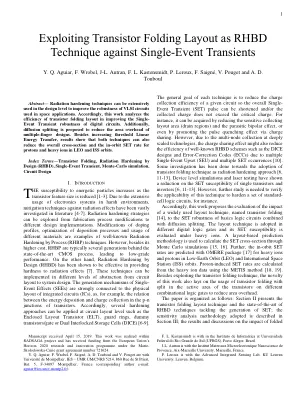

随着晶体管特征大小的降低,对能量颗粒的敏感性会增加[1-3]。由于电子系统在恶劣的环境中的广泛使用,对辐射效应的缓解技术已在文献中得到了大量研究[4-7]。可以从制造过程修改到不同设计实现的辐射硬化策略。修改掺杂曲线,对沉积过程的优化和使用不同材料的使用是按过程(RHBP)技术众所周知的辐射硬化的示例。但是,除了其较高的成本外,RHBP通常是最先进的CMOS流程后面几代人,导致低级性能。另一方面,通过设计(RHBD)进行辐射硬化可有效提供对辐射效应的硬度[7]。这些技术可以从电路布局到系统设计的不同级别的抽象级别实现。单事件效应(SEE)的产生机制与综合电路(ICS)的物理布局密切相关,例如,在晶体管的P-N连接中,能量沉积和电荷收集之间的关系。因此,可以在电路布局级别上应用几种硬化方法,例如封闭的布局晶体管(ELT),防护环,虚拟晶体管/门或双互锁存储单元(DICE)[6-9]。

利用晶体管折叠布局作为RHBD技术针对单个事件瞬变

主要关键词