机构名称:

¥ 1.0

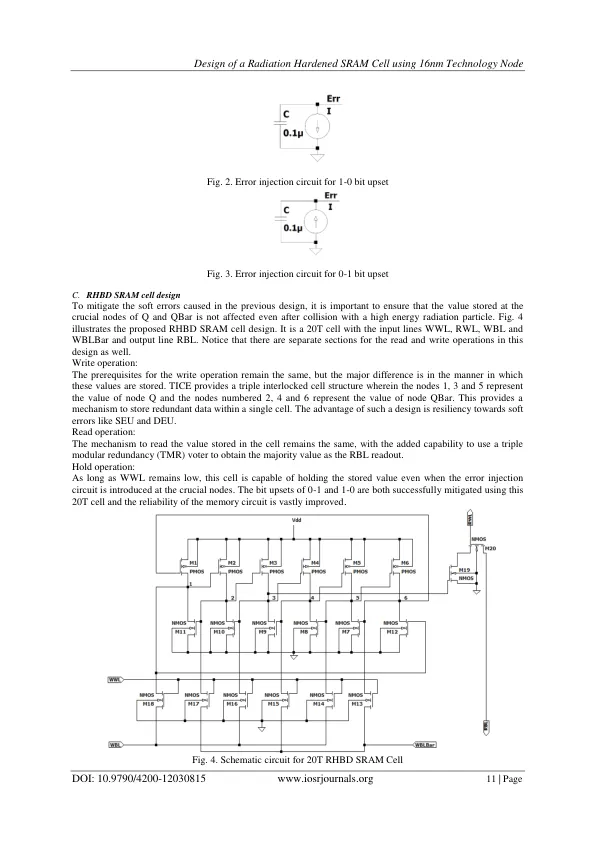

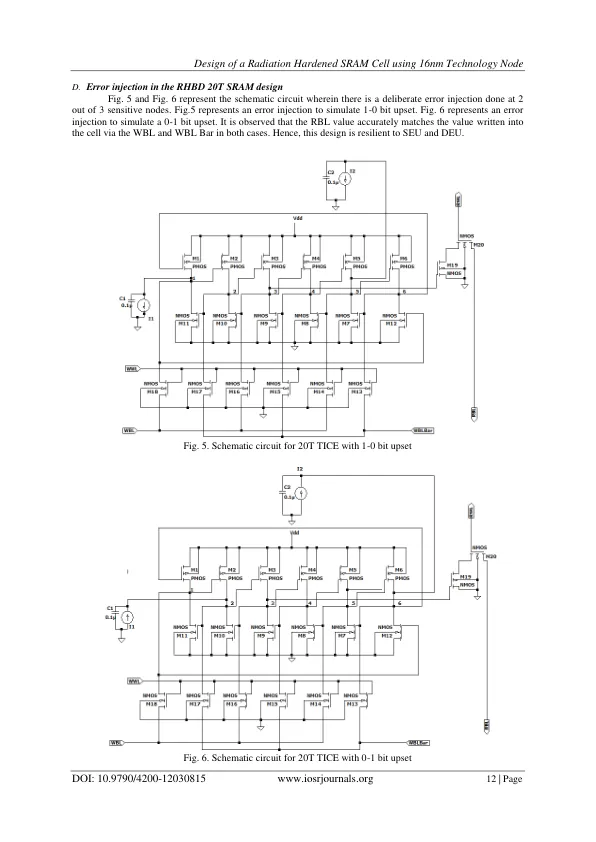

与过去的技术节点相比,器件的缩小可能会导致常规(未硬化)六晶体管 (6T) SRAM 单元的 SEU 敏感度增加 [8]。尽管 SEU 是一种非破坏性事件,但 SEU 概率的增加可能会对更大规模 SRAM 器件的使用造成越来越大的问题。这在使用高性能数字信号处理器的商用现货产品、太空任务和核电反应堆中尤其如此。由于多个位翻转可能导致同一个字中出现多个错误,因此这是一个更大的问题 [9]。在本文提出的设计中,标准 SRAM 单元经过辐射硬化处理,以减轻 SEU 和 DEU。TICE 存储单元可以自我纠正最多两个同时发生的翻转。为了进一步提高整体可靠性,我们应用布局技术将关键节点尽可能地放置在 TICE 存储单元中。在假设三个同时发生的翻转很少见的情况下,这降低了关键节点同时被击中的可能性。与标准 8T 存储单元和 DICE 存储单元相比,本研究提出的存储单元具有更高的耐辐射性。

采用 16nm 工艺设计抗辐射 SRAM 单元...

主要关键词