机构名称:

¥ 1.0

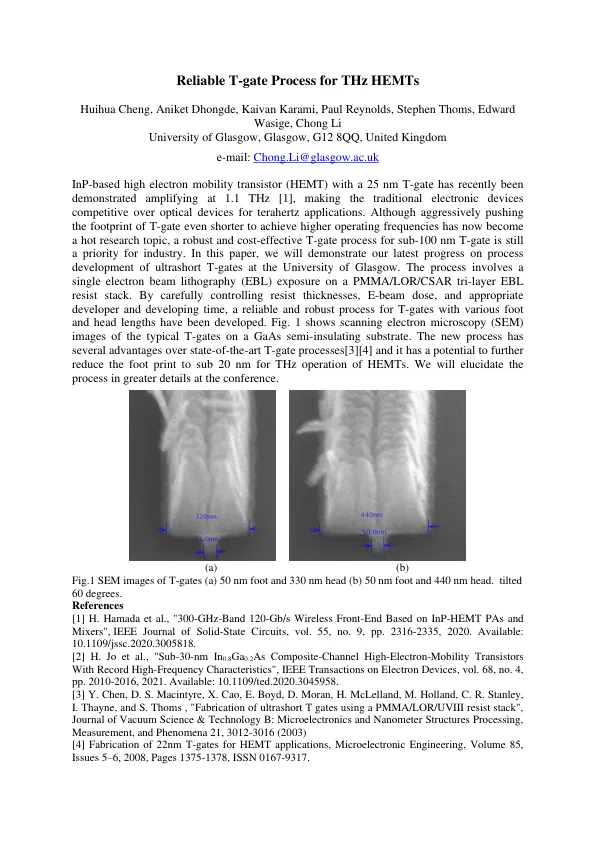

最近,具有 25 nm T 栅极的 InP 基高电子迁移率晶体管 (HEMT) 已被证明可在 1.1 THz 下放大 [1],这使得传统电子设备在太赫兹应用方面比光学设备更具竞争力。尽管积极推动 T 栅极的占用空间变得更短以实现更高的工作频率现已成为热门研究课题,但针对 100 nm 以下 T 栅极的稳健且经济高效的 T 栅极工艺仍然是行业的首要任务。在本文中,我们将展示格拉斯哥大学在超短 T 栅极工艺开发方面的最新进展。该工艺涉及在 PMMA/LOR/CSAR 三层 EBL 光刻胶堆栈上进行单次电子束光刻 (EBL) 曝光。通过仔细控制光刻胶厚度、电子束剂量以及适当的显影剂和显影时间,我们开发了一种可靠且稳健的工艺,用于具有各种脚和头长度的 T 栅极。图 1 显示了 GaAs 半绝缘基板上典型 T 栅极的扫描电子显微镜 (SEM) 图像。与最先进的 T 门工艺[3][4]相比,新工艺具有多项优势,并且有可能将 HEMT 的 THz 操作占用空间进一步缩小至 20 纳米以下。我们将在会议上更详细地阐述该工艺。

适用于 THz HEMT 的可靠 T 门工艺 - Enlighten Publications

主要关键词