机构名称:

¥ 1.0

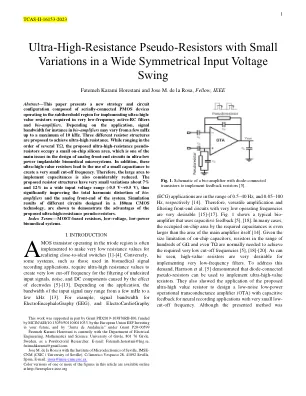

摘要 — 本文介绍了一种具有自定义指令集架构的嵌入式可编程处理器的设计和实现,用于高效实现人工神经网络 (ANN)。ANN 处理器架构可扩展,支持任意数量的层和每层人工神经元 (AN) 数量。此外,该处理器支持具有任意 AN 间互连结构的 ANN,以实现前馈和动态循环网络。该处理器架构是可定制的,其中 AN 之间的输入、输出和信号的数值表示可以参数化为任意定点格式。本文介绍了一种设计的可编程 ANN 处理器的 ASIC 实现,用于具有多达 512 个 AN 和 262,000 个互连的网络,估计占用 2.23 mm2 的硅片面积,在 1.6 V 电源下以 74 MHz 运行,采用标准 32 nm CMOS 技术,功耗为 1.25 mW。为了评估和比较所设计的 ANN 处理器的效率,我们设计并实现了专用的可重构硬件架构,用于直接实现 ANN。本文介绍了所设计的可编程 ANN 处理器和 Xilinx Artix-7 现场可编程门阵列 (FPGA) 上的专用 ANN 硬件的特性和实现结果,并使用两个基准进行了比较,即使用前馈 ANN 的 MNIST 基准和使用循环神经网络的电影评论情绪分析基准。

具有定制的人工神经网络处理器...

主要关键词